利用单板三维立体空间已成为解决高密单板布局的 有效方法,立式表贴模块作为单板高密布局的一 种解决方案,已在业界相关产品中得到应用(如 立式电源模块/厚膜等),而布局在立式表贴模块上的表贴元 器件种类也会越来越多,本文通过试验设计和分析及仿真 模型的建立,对立式表贴FR4模块上表贴陶瓷电容、SOT/SOP器件及MLF器件缺陷预防模型进行分析。

前言

随着信息社会宽带化的推进和3G时代的到来,宽 带、NGN等核心网络汇聚层产品的容量越来越高,提高单 位面积用户数量可有效降低设备成本,增加产品竞争力, 但同时会带来单板局部高密的问题。利用单板三维立体空 间已成为解决高密单板布局的有效方法,例如固网高密宽 带用户板Line Driver(线路驱动)部分、缓启动部分均可使 用立式模块。业界也有二次电源将保险管、大电感组装到了表贴立式模块(见图1)。

但是,在立式模块实际生产过程中,器件在二次回流 时存在偏位/掉件等风险。本文通过试验及仿真模型,重点 对不同封装器件在表贴立式FR4模块上二次回流发生偏位/ 掉件情况进行研究,在设计阶段采取针对性措施避免上述缺陷的发生。

相关理论介绍

众所周知,回流焊接过程中,随着温度曲线的改变, 在焊盘、锡膏、元件焊接端面三者之间发生了复杂的物理 及化学的反应。二次回流时防止元件掉落方面需注意元件 重量、有效焊接面积、器件重心、器件布局方向等方面的 因素。

1、焊点力学模型分析

从焊点的力学模型分析开始进行分析。锡膏熔融时,根据Laplace Young方程,在焊点的界面有这样的受力形态:

为液体表面所承受的压力差,

为液体表面所承受的压力差, 为液体的表面张力系数(定义为单位长度上作用的力,其单位为N/m),

为液体的表面张力系数(定义为单位长度上作用的力,其单位为N/m),  和

和 分别表示曲线在正交方向上的两个曲率半径。

分别表示曲线在正交方向上的两个曲率半径。

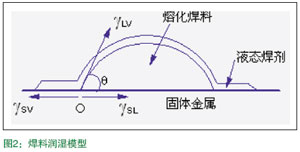

对于发生在固液之间的焊料润湿情况,可以用Young方程描述(参见图2):

2、双面回流单板二次回流理论研究

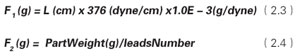

业界对单板第一次回流面器件掉件的情况有一些相 关研究【3】,根据表面张力和重力平衡原理计算力的平衡 【4】,当 时,可以判断为不会掉件;F1及F2计算公式见公式2.3及2.4。

对于二次回流时第一回流面器件,单位引脚所受表面 张力  (L为引脚与焊盘接触周长),熔融状态下焊 料的表面张力系数

(L为引脚与焊盘接触周长),熔融状态下焊 料的表面张力系数  为0.376(J/m2)。 业界有一经验公式【5】【6】【7】用于判断二次回流是否掉件:

为0.376(J/m2)。 业界有一经验公式【5】【6】【7】用于判断二次回流是否掉件:

关于重量面积比,G为元器件重量,S为总焊盘面积。 进行双面板的二次回流时,如果熔融焊料能润湿焊盘,在 液—固界面上的粘附力会大于内聚力(熔融焊料内部),所 以在二次回流时,熔融焊料内部应该是掉件的最薄弱位置。 当  元器件在二次回流时不会掉件;当

元器件在二次回流时不会掉件;当  焊料充分熔融时就会掉件;其中,

焊料充分熔融时就会掉件;其中, 是熔融焊 料的抗拉强度,是熔融焊料在断裂前能承受的最大张力强 度(单位面积力);

是熔融焊 料的抗拉强度,是熔融焊料在断裂前能承受的最大张力强 度(单位面积力); 与熔融焊料的内聚力或表面张力成正比,取决于熔融焊料在某一温度条件下的材料特性。

与熔融焊料的内聚力或表面张力成正比,取决于熔融焊料在某一温度条件下的材料特性。

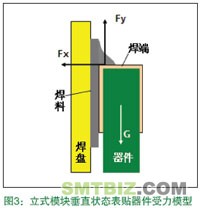

3、垂直过回流时表贴器件掉件理论分析

参考双面回流单板相关理论分析,在垂直状态下,表 贴器件同样受表面张力和重力作用,但与双面回流时第一 次回流面器件受力平衡状况略有不同,垂直状态下器件得 以保持平衡还与力矩有一定关系,并且焊料由于自身重力 和器件重力的作用(还包括润湿力,但润湿力在水平状况 与垂直状态也有稍许不同),会在较大的焊盘上流动,给 器件带来一定的运动惯性。因此,垂直过回流时表贴器件的受力分析较为复杂(参见图3)。

假定焊料与器件和焊盘已完全润 湿,在PCB焊盘上停止了流动,此时 表贴器件的偏位或掉件,也应有如下 条件:当 ,立式模块上器件在 二次回流时不会掉件;当

,立式模块上器件在 二次回流时不会掉件;当 焊料充分熔融时就会掉件;其中T 是熔融焊料的剪切强度。

焊料充分熔融时就会掉件;其中T 是熔融焊料的剪切强度。

试验研究

1、要因分析

立式表贴模块在组装到PCB上回流时偏位/掉件的影响 因素众多,绘制鱼骨图分析如下(见图4): 针对正常有铅组装过程中的立式HASL表面处理的FR4 模块上表贴器件情况,对表贴器件偏位/掉件的影响因素, 如器件选用、器件布局方向以及焊盘设计等定义为试验因 子进行研究。

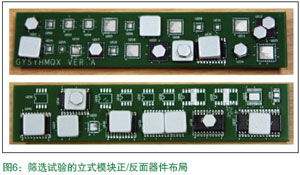

2、器件筛选和组装过程 分别针对陶瓷电容和SOT、SOP封装器件及MLF封装 器件进行研究。选取典型陶瓷电容、SOT封装器件和SOP及 MLF封装Line Driver芯片按照器件重量面积比进行筛选,根 据缺陷判断标准检验二次回流后情况,选择合格率为100% 的器件进行大量样本验证试验。

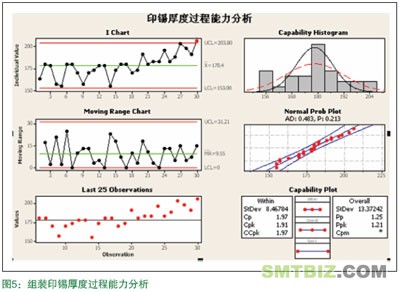

试验按照正常生产的条件分别进行一次组装和二次回 流。一次组装为0.15mm钢网设计,按规范开口,印锡和回 流参数按生产标准设置。为确保一次组装质量,安排在稳 定性较好的高复杂线体进行。

印锡过程能力分析如图5所示。

一次和二次回流曲线按正常炉温曲线设置,即回流40~80s,最高温度210~235℃。

3、筛选试验结果

A、Chip器件验证结果:验证试验表明水平布局时 SC1812及以上封装不适合大批量模块组装应用。垂直布局 时,SC2220电容和重量面积比为0.019及以下的SOT器件在 立式模块上二次回流无偏位缺陷;

B、SOT器件验证结果:垂直布局时,重量面积比为 0.019及以下的SOT器件在立式模块上二次回流无偏位缺 陷;

C、SOP封装器件验证结果:当SOP器件水平布局时, 按照重量面积比维度临界条件在0.27g/mm2,而当SOP器件 垂直布局时,按照重量面积比维度临界条件在0.37g/mm2。 垂直布局有助于减小SOP器件在立式模块上二次回流产生偏 位/掉件风险;

D、MLF封装器件验证结果:当SOP器件水平布局 时,按照重量面积比维度临界条件在0.157g/mm2,而当 SOP器件45度布局时,按照重量面积比维度临界条件在 0.157g/mm2。45度布局对于减小SOP器件在立式模块上二次回流偏位/掉件风险没有太大的帮助。

4、DOE试验

根据要因分析,在设计阶段主要影响因子是焊盘和布 局设计。

A、Chip元件试验设计

a.在DOE试验中,对chip器件焊盘和布局分别取两水平,如表1所示。

对试验结果进行分析,可知布局设计对偏位/掉件的影 响较大,布局垂直布局优于水平布局,焊盘设计1:1设计优 于1:1.2设计(参见图7)。

b.推力试验:对DOE试验陶瓷电容焊盘做推力试验, 从测试结果看,同样条件的剪切力有较大偏差,剪切断面 均是电容本体焊端被拉掉,说明焊点强度比器件本体强度大,焊盘设计对器件可靠性并无明显影响。

B、SOT器件试验设计

对SOT器件布局设计取三水平,焊盘设计取两水平,如表2所示。

从质量检验的角度看,仅有水平布局时的SOT偏位比 较大。考虑SOT器件偏位不易目检判断,对SOT器件回流前 后进行了三座标测试,对结果计算后进行偏位量分析,所得主效应图和交互作用如图8所示。

从图8可知,SOT器件1:1焊盘设计优于1:1.2焊盘 设计;布局的优先顺序依次为垂直1-水平-垂直2(参见 图9)。但从目视外观看,垂直2的引脚、散热焊盘都正常 搭在焊盘上,不如水平状态有比较明显的偏位出现,从质量可接受上来讲还是优于水平布局的。

两水平三因子试验及结果参见图10。 从因子主效应图上来看,器件布局方向及引脚数目对 结果影响较大,当重量面积比相同时,器件引脚数越多,失效率越高。垂直布局相比于水平布局失效率较低。

Chip元件垂直回流焊仿真模型

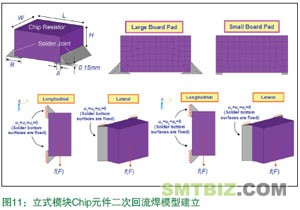

Chip元件仿真模型的建立

由于焊料在液态情况下的物理参数业界尚无相关的数 据支撑,并且垂直状态下的器件在焊料熔融状态下是一个 动态过程,因此目前尚无法定量的进行仿真模型的建立。 因此根据前期chip元件在立式模块上的实验结果作为仿真模型的输入。

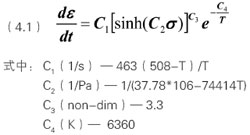

仿真模型使用焊点的蠕变方程进行仿真,采用有限元 模型中的Solid185单元结构,选取8个节点,三个自由度  ,对于焊料的相关参数赋予较小的数值用 于模拟其在回流焊熔融状态时的相关特性,蠕变应力下保 持120秒。通过chip元件的位移

,对于焊料的相关参数赋予较小的数值用 于模拟其在回流焊熔融状态时的相关特性,蠕变应力下保 持120秒。通过chip元件的位移 及剪切应变强度

及剪切应变强度  这两个参数来判断器件偏位的程度。

这两个参数来判断器件偏位的程度。

元件垂直和水平布局模型分析

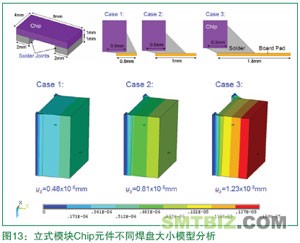

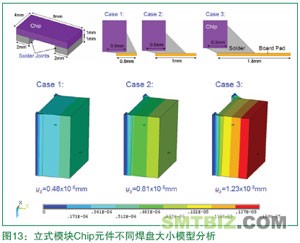

为方便进一步分析,将模型简单化,只考虑锡膏与元件无外围焊缝(fillet)连接,模型见图12。

1、Case1及Case2分别为普通熔融状态下,chip元件 在水平及垂直状态下的模型,通过模型计算,其向下的位 移分别为0.00201及0.00169,可见,垂直布局相比于水平 布局,器件的偏位风险较小。

2、为了进一步解释水平布局和垂直布局的差异,对 chip元件无锡膏一侧进行固定,使器件只受到重力作用,去掉由于旋转趋势造成的剪切力,见Case3及Case4,示意图如下图所示。其位移分别为0.00165及0.00163,以上两个数据基本相同。可知,垂直布局及水平布局的差异主要原因在于元件旋转趋势所形成的剪切应力造成。

3、对垂直布局的元件取消其重力作用,在元件上 方施加拉力,在元件的下方施加压力,做仿真模型,即Case 5,可得其位移量为0.00002,结合Case4的位移量0.00163, 其合力为0.00165mm,与正常模型的位移 0.00169mm差 0.00004mm,可见正常模型的受力除了元件的重力和旋转趋势 的剪切力外,还由于这两个力的综合作用产生了一些影响。

4、通过将Case2的上下两个锡膏合在一起进行仿真, 见Case6,发现其位移量非常接近Case1,也 说明了垂直布局和水平布局的根本差异在于锡膏对元件的剪切力造成。

不同锡膏厚度及焊盘大小的影响

通过对不同锡膏厚度0.1mm、0.125mm 及0.15mm的chip元件在水平布局和垂直布局 两种状态下的剪切应变做仿真分析。从结果来 看,同样重量面积比下,锡膏厚度越大,及元 件的离板高度越大,模型的剪切应变值越大, 对应的元件偏位掉件风险也越大。结合模型相 关结果,元件的离板高度越大,相应的旋转趋 势也越大,则元件的偏位风险也越大。

通过建立chip元件分别在0.5mm、1mm 及1.8 mm 不同焊盘大小下的仿真模型, 结果如下图所示, 0.5 mm 焊盘的位移量 为0.00004 mm , 1.0 mm 焊盘的位移量 为0.000081 mm , 1.8 mm 焊盘的位移量 为0.000123 mm , 可知, 越大的焊盘设计会增加元件的偏移量,相应的偏位风险也会越大。

究其原因,主要原因为元件焊盘越大,锡膏的体积也 越大,元件焊端底部的锡膏高度也会越大,相应的元件的离 板高度越大,根据模型的结果及相关分析,元件的离板高度 越大,旋转趋势的剪切应力也越大,因此元件的偏位风险也 越大。

结论

对表贴立式FR4模块上表贴元器件进行组装试验可得出 如下结论:

1、 对水平布局的SOP 封装器件, 重量面积比 <0.027g/mm2时,验证试验无偏位/掉件缺陷;

2、 对垂直布局的SOP 封装器件, 重量面积比 <0.037g/mm2时,验证试验无偏位/掉件缺陷;

3、 对MLF封装器件,重量面积比<0.0147g/mm2时,验证试验无偏位/掉件缺陷。

仿真结果与实际实验结果基本一致,其表现出来的相 关趋势和试验数据也一致:

1、重量面积比越大,其失效概率也越大;

2、器件垂直布局有助于失效率减小;

3、同样的重量面积比下,焊盘越小,失效概率也越小;

4、同样的重量面积比下,锡膏厚度越大,失效概率也越大。

参考文献