百万闸FPGA设计中PC系统的测试基准

中国工程师已经开始采用百万闸级FPGA设计产品,那么什么样的PC系统才能满足百万闸级FPGA的综合和布线对计算能力的需求,看完本文后你将会有一个较清晰的概念。

James Lee

首席顾问工程师

Intrinsix公司

Bob Peterson

自由撰稿人

在FPGA的设计平台的测试过程中,标准测试电路包括太阳微系统(Sun Microsystems)公司的picoJava处理器,利用Synplicity公司的Synplify综合工具和赛灵思(Xilinx)公司的Alliance布线工具,可以将picoJava处理器嵌入Virtex 1000 FPGA之中。此外,还可采用ASIC设计中常用的Talisman源代码(hod)设计作为测试基准。

测试源代码

要对EDA平台进行测评,必须寻找合适的测试代码。这些测试代码必须具备免费获得的渠道,否则其它测试人员难以重复测试,也就是说,要么拥有测试代码,要么采用开放的公共源代码。

这些测试代码的规模和复杂度必须与待测试的平台相适应。藉由Sun公司的网站www.sun.com申请许可,就可下载各种测试代码。各种IP的许可条款有所不同,但通常情况下,SCSL(Sun小区源代码许可)允许在最初的评估和开发阶段免费使用源代码。

测试之前,要从网站上下载picoJava内核,它由一个小型微处理器构成,可直接执行由Java虚拟机定义的Java字节码指令,picoJava的原始字节码能提高执行效率。我们选择picoJava-II作为EDA平台测试,它包括picoJava-II编程参考手册、软件开发环境、仿真环境、RTL设计文件、验证测试套件、代码范例和包含177Mb源代码和文档的RTL文n。部份文n是HTML文件,可用Web浏览器来浏览设计中的Verilog层。

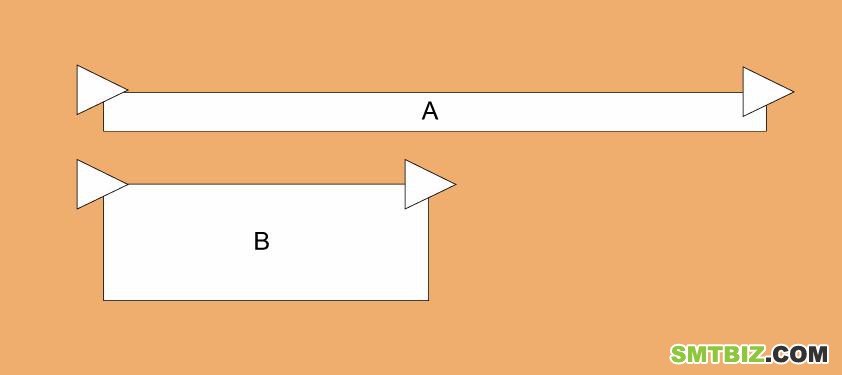

通常,picoJava内核代码很大,直接应用到FPGA中比较困难,要将代码适当简化。太阳公司将FPU和缓存指定为可配置的模块,如图1所示为picoJava模块图修改后的结果,最终的picoJava基准包含649,770个门。

Talisman测试基准和百万闸FPGA

经验证明,EDA工具的性能和硬件平台对设计有很大的影响。因此,尽管picoJava是FPGA设计流程的理想测试基准,我们还要从ASIC标准链接库中选择Talisman源代码。Talisman是微软和Cirrus Logic共同开发的一个图形引擎,微软免费提供大部份关键源代码(hod)用于基准测试项目。现有的Talisman 源代码的规模太大,难以嵌入到FPGA中,首先将门数减到946,400,进一步再减到396,800,它们的Verilog代码可从www.isdmag.com/edabenchmark下载。

946,400门的Talisman源代码需要利用100%的FPGA资源,称其为Talisman_100,相比较而言,396,800门只需要利用60%的FPGA资源,因此称为Talisman_60,它代表更为现实的设计。

我们选择的目标FPGA是赛灵思公司Virtex系列XCV1000,它包含1,124,022个系统门(27,648个逻辑单元)、512个用户I/O引脚以及4个可提供准确时钟分配的数字延迟锁相环(DLL)。据称其时钟-输出延迟小于3ns。

在Virtex结构中,FPGA的可配置逻辑块(CLB)位于芯片的中央,周围是RAM模块、I/O互连区(VersaRing)、可配置逻辑和I/O模块。在Virtex的CLB中,查找表、多路再使用器、触发器和其它组成部份在每个CLB中复制4次。为了便于布线,每一个CLB有两部份。

利用这种结构的FPGA资源实现通用电路,需要专门的综合和版图设计支持。如前所述,可以采用Synplicity公司的Synplify工具进行综合,而用Xilinx公司的Alliance布局和布线工具进行版图设计。Alliance工具的独特功能包括代码翻译、映射、时序分析、布局和布线以及最终的时序分析。

GUI的考虑

相对于ASIC设计来说,FPGA设计工具稍微不同。FPGA工具更加着重于图形用户界面(GUI)的使用。因此,Synplify和Alliance工具的使用比大多数ASIC工具都容易,但是批处理工作模式并不总具备无缝连接的特性。

例如,以批处理方式进行试验时,发现Synplify工具不能从网络服务器上导入设计文件。Synplify工具的GUI在交互运行时,不存在检索文件问题,并且从本地磁盘上导入设计文件也不存在问题。因为我们总是从计算机的磁盘上运行基准测试程序以避免网络阻塞造成的故障,此外,当藉由键盘从Synplify工具退出时,NT的任务监视进程表仍然显示该任务持续执行了几分钟,表明系统难以退出运行状态。可是,当Synplify完成一次正常运行后,程序就会立刻退出,因而能记录精确的运行时间。

让Alliance自动运行存在一些问题,因为现在还不能以批处理命令控制所有功能。然而,可以藉由宏来实现这些功能,并用脚本初始化该宏。在标准测试程序中,无法实现Alliance的时序分析器功能,因为在退出时该工具弹出一个对话框,询问是否确认退出,而批处理文件却不知道如何选择“是或否”。

脚本对基准测试过程十分重要,我们仔细嵌套的各种脚本还具备一致测试工具执行时间的基础。如果设计工具不能及时退出,我们就无法精确计时,于是只能把时序分析器放在基准测试程序之外。

如果不进行基准测试,当设计过程很短且迭代次数较少时,就可更多地依赖GUI。开发只使用几次的脚本之目的在于,以工程师期望的方式设置FPGA工具,其运行也只是几次而已。

传统的FPGA比较小,足以实现快速的设计流程,但是,随着FPGA容量的提高,特别是百万闸FPGA的出现,要求广泛采用依赖于批处理模式的计算机农场(computer farm)。

桌面计算机的配置

为了完成FPGA设计任务,桌面计算机要做如下标准配置: 550MHz Compaq SP700、单Pentium III Xeon和1Gb的DRAM;550MHz IBM Intellistation Z Pro、双Pentium III Xeon处理器和2Gb的DRAM;400MHz双Pentium III Xeon PC、512Gb的DRAM;300MHz Pentium II PC、512Gb的DRAM。

所有这些系统均运行Windows NT4,且具有100MHz的总线(300MHz的计算机除外,它具有66MHz总线)。400MHz PC代表另一种典型配置。Compaq和IBM允许我们使用其计算机进行测试。

由于FPGA基准测试设计比大多数用于ASIC基准测试的设计小,我们希望所用的PC能够完成规定的EDA设计任务。

实际上,这些PC完成综合和版图设计任务的速度很快,但是,128MB的DRAM还是不足以处理百万闸级FPGA设计。

我们只测试了一台内存较小的400MHz PC,这台机器综合较小的Talisman代码基准程序耗时约23分钟,而其它拥有512MB DRAM的400MHz PC只需14分钟。128MB的计算机布局和布线要花费63小时,而512MB的计算机在4小时内就完成了版图设计。

本文总结

具有适当容量DRAM的PC(根据ASIC设计标准)可很好地处理FPGA设计任务,这个结论具备极好的可预测性。实际上,这标志着系统配置和基准测试之间存在一定的关系。

在综合过程中,两台550MHz PC的性能基本相同。象通常的基准测试一样,在每一个测试平台上将程序运行3次,然后取平均。IBM和Compaq 550MHz机器的实际运行时间仅相差1/10秒,在测试精度范围之内。

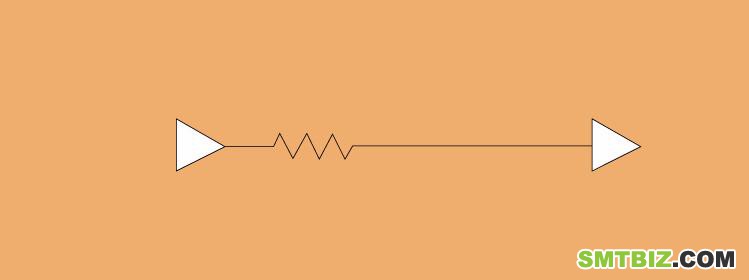

400MHz和300MHz基本配置的PC性能卓越,非常接近于其处理器速度。400MHz PC比550MHz PC慢27%,且基准测试性能降低了26%到23%,类似地,300MHz比550MHz约慢45%,基准测试性能降低了41%到37%。如图2所示。

实际上,即使在最慢的计算机上运行最大的设计(如在300MHz PC上运行picoJava),Synplify工具只需运行81分钟就可综合1百万闸的FPGA,在最快的机器上时间可缩短到47分钟。无论何种方法,都可以在1天之内完成百万闸级FPGA综合。

作者James Lee是Intrinsix公司的首席顾问工程师,他具有12年的Verilog工作经验。Bob Peterson是自由撰稿人,在过去的17年间曾为许多杂志和公司撰写各种技术专题。