By 张兴隆

传统模拟在电路技术通常用于判断组装 PCB 是否有缺陷。这些缺陷包括短路、器件立起、或者器件放置错误。模拟在电路测试 (ICT) 的功能就是藉由自动测试程序 (ATPG) 生成错误器件纠正报告。自从 1972 年起,这种测试方法就成为无源器件测试的根本方法,但现在这些方法正受到电子器件封装改变而带来的威胁。

现今所用无源 SMD 的最小尺寸已达 0.5mm×1mm ,表面黏着器件又在器件底部隐藏了节点,硅片封装已经迈向细间距、超细间距和 BGA ,而 500 至 750 脚的封装也已出现。

采用 SMD ,就没有可以用来探测的器件引脚。探测只有藉由过孔来进行,而通常线路板两面都需要探测。如果在电路节点上找不到过孔,就要人为增加测试点。但现今开发者既面临巨大的“尽快上市”压力,同时器件可能比测试点还要小。因此可测试性设计 (DFT) 常常被抛在一边,既便有测试点,也很少会加上。

PCB 上的线径一般为 0.1mm 宽,过孔则“埋在”内层里,根本没有接触的可能。此外,探针的尺寸并不随着与其接触的焊盘尺寸的缩小而成比例缩小。焊盘已由 1mm 缩至 0.1mm ,而相临探针的中心点间距已从 2.54mm 降至 1.27mm ,仅缩小了一半。

传统的 ICT

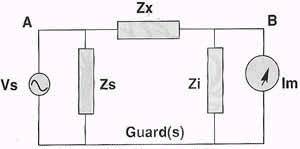

模拟在电路测试的基本技术是藉由受测器件 (DUT) 的一个节点对网络施加电压,而在该器件的另一节点上测量电流 ( 图 1) 。

图 1 :可接触节点的减少意味着将无法采用传统 ICT 技术测试与其相连的所有分支。

假设电压源 Vs 为理想电压源,并且可以供应 Zs 和 Zx 所需的足够电流;同时假定测量电流的 Im 是一个理想电流表,其插入损耗为零。所用的电流表常采用运算放大器的形式。设 Zi 两端的电压为 0 , Zi 也没有电流流过,则 Zx 的值为:

Zx=Vs/Im

如果节点 A 无法接触,那么就不能从 Vs 提供电流。如果电压源施加于相邻节点上, A 点的电压就无从知道,上面关于 Zx 的计算也就不可能了。

与此类似,如果节点 B 无法接触,也就不能够断定流过 Zx 的电流。在相邻节点测量电流会使流过 Zi 的电流不为 0 ,从而导致电流测量不准确。最后,如果保护节点也不能接触到,则在 Zx 两端会有一等效阻抗,改变了公式 1 的计算。因此,在电路中漏掉任何一个节点都会使得该器件无法测试。

受限接触测试技术

模拟 ICT 的主要优点是 ATPG 、诊断准确。如果满足下面两种条件,这些优点在接触受到限制时也可以保留下来。第一,先从小激励电压的弱加电测量开始,同传统 ICT 方法一样。弱加电测量将电路拆成小部份,使得分析可以很快完成。在小电压下,硅器件的阻抗大到等同开路,可以形成不连或仅有一个节点相连的几组模拟器件。现代电路设计中,这些器件组尺寸有限,而且通常都是隔离的。第二个条件与每个器件组最大的器件出错数量有关。将整个电路板分为一个个器件组效果非常好。对一个接触受限的电路来讲,如果有几处缺陷同时存在,那是无法准确断定的。因此为得到正确判断,必须限定器件组内缺陷的数量。

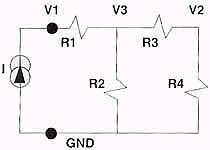

图 2 :这个条件可能显得有些限制,它相当于大多数制造商遇到的最糟情况。

藉由示例 ( 图 2) ,我们可以很容易明白新的 ICT 测量技术。这里,受试电路 (CUT) 由电阻 R1 到 R4 组成,电流源 I 是与测试系统相连的激励电流, V1 、 V2 和 V3 是各节点相对 GND 测得的电压。当电路器件都等于标定值时,节点电压也就定义为标定值 ( 公式 2) 。

Δ V1=V1-V1 \/\/noia\/\/ Δ V2=V2-V2 \/\/noia\/\/ Δ V3=V3-V3 \/\/noia\/\/

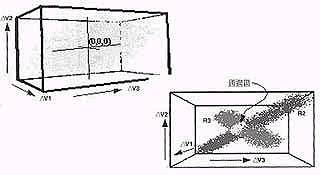

首先让我们来看一下,当激励源 I 保持恒定,而器件可以在整个允许误差范围内变动时,该电路的表现情况。这里的范围可以很容易地由任何标准仿真套件来制定,如能进行 Monte Carlo 分析的 HSPICE 。如果从每个仿真的Δ V 值减去标定电压,可以将每次仿真结果的值绘制成曲线 ( 图 3a) 。

图 3 :这是 10,000 次仿真结果图形,都在一个限制方框里,方框中心定为 (0,0,0) 。

仿真合格

藉由检查节点电压变化是在着色区域内还是在着色区域外,可以判断一块电路是合格还是不合格 ( 图 3a) 。如果节点电压变化是在区域外,那么该电路就是不合格的,实际失效器件数目可再单独确定。

假如所有器件允许在± 100% 范围内变化,则仿真合格的结果在外形上很相似,但数量却要大得多 ( 图 3b) 。曲线并未提供有关失效原因的进一步情况,有人也许会问:限制错误的数量为什么能增加图线的信息量?这正是获得诊断信息的关键。

在图 3b 中,还有两组被仿真的电压值画于图 3a 中。每个器件都是 5,000 次仿真的结果。标有 R2 的一组电压值是藉由将 R2 随机地由 0 变化到无穷大而得到的结果,同时去除处于误差范围内的 R2 值。其它器件则在各自相应的范围内变化。还有为 R3 而测量的一组类似的电压值,也采用同样的技术。为清楚起见,器件 R1 和 R4 则都省掉了。

当Δ V1 、Δ V2 和Δ V3 的变化限于这些区域中的任一个时,就可以作出诊断。只要每个器件都有各自不同的区域,就有可能找出出错的器件;一旦出错器件找到了,可藉由直接了当的方法找出因器件值而引起的节点电压的具体变化。

如果所有器件的区域没有太大区别,则会有多个器件同时落入 R2 或 R3 等区域内,于是诊断结论就是“该区域有一个或以上的器件出错”。因为无法知道是一个器件出错还是一组器件出错,因此假定其它器件而对某个器件值进行计算是没有多大价值的。

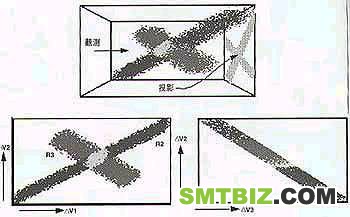

受限节点接触

前面我们只讨论了所有节点都可以测量的情况,但有时会有多个节点无法接触,比如 V3( 图 4a) 。当无法接触 V3 时,我们只能观测 V1 和 V2 的电压,所见到的是包括 V1 和 V2 在内的对象在平面上产生的“投影”。虽然形状上有些微差异,但 R2 和 R3 仍然是可以区别的 ( 图 4b) 。

图 4 :由于接触点受到限制,必须从另一角度来观测失效器件。比如从箭头所指的节点 V1 和 V2 来测量。

假设另有一组节点可以接触,比如 V1 和 V3 ,这相当于从下往上观察图 4b( 图 4c) 。这里因 R2 或 R3 改变产生的电压值是不易区别的,从观测中无法辨别关于出错器件的信息,只能鉴别出整个范围内的正确或出错部份。

测试点选择

为得到明确的诊断,测试点的选择很重要。在某些情况下,只要有少量器件能被指示出来就是可以接受的;而在另一些情况下,适宜地选择测试点可进一步缩小被测器件组数目。

在任何情况下,所作选择都应该与器件误差容限、器件值,甚至器件类型无关,而应完全根据器件内部连接,即线路拓扑结构。这样就可以判断何处需要增加测试点,或在设计中添加一个器件以省掉一个测试点。

发展方向

与传统 ICT 不同,这种测试法能方便地扩展到有源器件的全加电测试,这种扩展也包括 ATPG 。有源器件的参数变化同样可以很容易地仿真,并确定明确的区域。注意,测试一个线路并不需要知道电路的关键参数,只需了解联机布局即可。如果电路节点电压不在合格区域内,而电路装配是正确的,那么一定有器件值超出容限范围。

关键参数必须藉由设计来保证,或经功能测试来筛选。几乎所有关键参数都能表示为某些节点电压的函数,因而可大大减少所需的功能测试数量。

与标准兼容

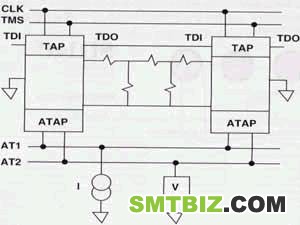

采用数字电路边缘连接器功能测试来生成和开发有效的诊断,费用很高。在数字节点的接触受到限制时,需采用数字边界扫描 (IEEE1149.1) 技术。用于模拟测试的一个类似标准 (P1149.4) 也正在出现。该标准确定了一种藉由 AT1 总线为 P1149.4 兼容器件的管脚分配电流激励的方法,以及藉由 AT2 总线测量管脚电压的方法 ( 图 5) 。

图 5 :所述的受限接触点测试技术与 P1149.4 标准相符,并且大大扩展了器件周围以及器件之间可测试的网络范围。

在图 5 中,只要测试系统所采用的电流源不与电流规范一致,则开关电阻就不会有什么影响。将开关电阻与电压表输入阻抗串联,一般不会影响测量。

物理探测节点的减少并不意味着将会倒退到模拟功能测试,无法形成有效的诊断。虽然还远不能替代传统 ICT ,但是可以看到,在少得令人惊奇的探测节点上仍然能够获得有意义的结果。如果因测试点选择的困难而得不到明确结果,那么诊断组内的器件数目就要更少一些。