作者:Akito Yoshida, Barry Miles, Vladimir Perelman, Young Wok Heo and Richard Groover, Amkor Technology Inc., Chandler, Ariz. 2005-12-30

手机和其他一些应用需要更加创新的芯片级封装(CSP)解决方案。起先,小于0.8毫米间距的CSP和密间距球栅阵列封装(FBGA)已经能够满足要求。但是,PCB板和封装转接板的布线限制规定0.50或0.40毫米是CSP封装最小的实用间距,这使得在X和Y方向上提高封装密度非常困难。现在系统设计师为了手机和其他很多紧凑型消费品,不得不选择用3D封装来开发Z方向上的潜力。

手机经历了从只有基带处理器和非常有限内存的蜂窝手机到如今配置有其他功能处理器和内存的高端手机的演化,这样的发展把工业界推向了3D封装解决方案。

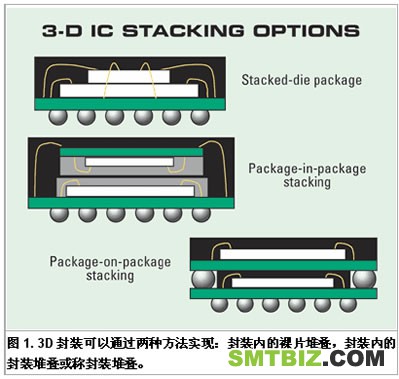

3D封装可以通过两种方法实现:封装内的裸片堆叠,封装内的封装堆叠或称封装堆叠(如图1)。两种方法各有利弊(见表1)。总体上说:

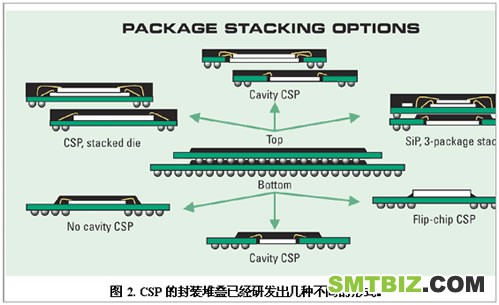

·因为裸片堆叠CSP在开发Z方向空间(即高度)的同时还保持了其X和Y方向上的元件大小(厚度即使增加也是非常小),这种封装已经被很多手机应用所接受。裸片堆叠CSP封装的主要缺点是,如果堆叠中的一层集成电路出现问题,所有堆叠的裸片都将失效。

·封装堆叠包括翻转一个已经检测过的封装,并堆叠到一个基底封装上面,后续的互连采用线焊工艺。封装堆叠的装配过程类似于裸片堆叠CSP。封装堆叠在印制板装配的时候需要另外的表面安装堆叠工艺。

"所有权"是困扰这些方法的一个难题。因为IDM厂商生产封装堆叠和裸片堆叠的CSP产品,OEM厂商就不必要另外地选择内存和逻辑集成电路,除非是专门研发出来的。另一方面,只要元件大小匹配,OEM厂商可以把任何内存集成电路的封装堆叠到另外一个逻辑电路封装上,即使这个逻辑电路封装由不同IDM厂商提供。虽然需要使用印制版装配线上的专门装配设备来堆叠封装,OEM厂商还是可以获得下至单个元件的系统配置灵活性。比如,OEM厂商能够就在最终产品堆出之前确定内存密度。

关键的装配技术

成功的3D封装是晶圆级和封装级核心技术发展和革新的结果。例如,芯片厚度的控制对于在封装堆叠解决方案中实现薄的模盖是非常关键的。对于晶圆的减薄, 背面研磨到100微米以下并不困难,但是,减薄工艺必须要进行优化以保证裸片的质量和可靠性。在晶片背面机械研磨过程中,硅晶粒形变很容易导致应力,并引发可靠性(例如裸片破裂)和工艺处理的问题(例如处理扭曲的晶片)。因此需要抛光来消除硅晶粒形变,目前已经提出了几种技术,例如CMP,湿刻蚀和等离子刻蚀。表2给出了在先进的晶圆减薄工艺下对裸片扭曲的控制和能够达到的表面粗糙等级。

线焊技术是决定封装堆叠模盖最小高度和S-CSP裸片堆叠高度的一个关键因素。裸片表面和模盖之间需要低的焊线成形高度和长的线焊间隙,这样相对裸片焊盘引出的导线来说窄小。只要间隙大于0.3毫米,就足够使用传统的球焊技术,这样使得高产率和优异的焊接质量成为可能。但是3D封装中的多裸片或多封装需要间隙小于0.3毫米,因此需要应用不同的线焊技术。

·球焊技术在被不断地改进以减小焊线成形的轮廓。

·支架型针脚焊接(SSB)首先使用球焊到焊针上,接着针焊接到已经有金接线柱的裸片焊盘上。这项技术在不损坏焊线的情况下允许焊线成形高度小于100微米。因为焊接步骤更多,这种焊接技术相比传统的球焊产率更低。

·金楔焊接能够做到焊线成形高度小于75微米,但是焊点间距必须大于典型的球焊接。

总的来说,在完成设计之前需要仔细研究衬底焊针的设计和线焊方法选择。

裸片堆叠技术

因为需要考虑更多的参数,在单个封装里装配多个裸片相对装配单个裸片需要更高级的技术。封装成本和性能,包括制造产量,机械强度,可靠性,散热和电学特性,都被总体封装设计所直接影响,在早期发展阶段需要特别的注意。

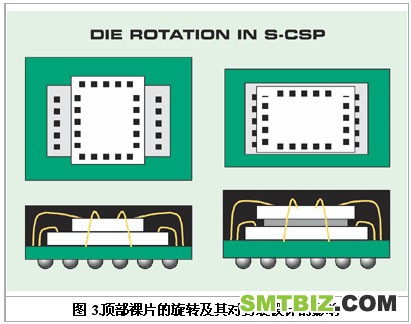

例如,一个问题可能是顶部裸片的旋转及其对封装设计的影响(参见图3)。虽然在一方面需要更大的封装,但是因为额外的布线面积可能需要采用低成本的设计规则。当有裸片悬在上方的时候,线焊和模成型成为具有挑战性的技术。但是两个裸片之间可能不需要间隔空间,因为下面裸片的焊盘可以足够远离边缘,这样能够允许焊接上面的裸片。这些类型的选择需要在衬底设计之前做出。

当裸片堆叠的复杂度增加后,选择适当的裸片堆叠和后续衬底的要求极大增加了每个新封装设计的复杂度。