1 前言

开展高密度、高精度板级电路模块表面组装设计、工艺技术与过程质量控制技术研究,制订高密度板级电路SMT工艺设计规范和标准,应用高精度、高密度板级电路的SMT组装技术,缩小常规板级电路面积达到或小于1/3,重量减轻1/3,部分电路模块能进一步扩展,促进和推动我国军事电子装备的板级电路组装上水平,实现趋于“零缺陷”组装和一次成功。

开展高密度、高精度板级电路模块表面组装设计、工艺技术与过程质量控制技术研究,制订高密度板级电路SMT工艺设计规范和标准,应用高精度、高密度板级电路的SMT组装技术,缩小常规板级电路面积达到或小于1/3,重量减轻1/3,部分电路模块能进一步扩展,促进和推动我国军事电子装备的板级电路组装上水平,实现趋于“零缺陷”组装和一次成功。

2 关键技术

(1)高密度组装PCB设计

主要包括应用0201元件、引脚中心距为0.3mm的QFP、球栅中心距为0.4mm的CSP等高密度细间距元器件的焊盘设计,元器件安装密度达25个/cm2,焊点密度达50个/cm2,高密度细间距PCB的设计。

(2)高密度组装工艺及质量控制技术

元器件中0201、0402元件属于超小型元件,QFP、TSOP 、BGA、CSP属于超细间距器件,整个PCB的元件安装密度高、间距小,焊点数量多,因此安装、焊接、检测工艺十分复杂,难度很高。

高密度组装工艺及质量控制技术研究的主要内容包括组装工艺路线,回流焊机的温度控制,焊膏印刷工艺(钢模板设计、钢模板开口设计、钢模板制作、焊膏材料选择),元器件贴装参数、焊接工艺技术、清洗工艺及质量检测(焊点形态检查——三维X光编程检测、测试焊点参数设置、检测结果统计)。

(1)高密度组装PCB设计

主要包括应用0201元件、引脚中心距为0.3mm的QFP、球栅中心距为0.4mm的CSP等高密度细间距元器件的焊盘设计,元器件安装密度达25个/cm2,焊点密度达50个/cm2,高密度细间距PCB的设计。

(2)高密度组装工艺及质量控制技术

元器件中0201、0402元件属于超小型元件,QFP、TSOP 、BGA、CSP属于超细间距器件,整个PCB的元件安装密度高、间距小,焊点数量多,因此安装、焊接、检测工艺十分复杂,难度很高。

高密度组装工艺及质量控制技术研究的主要内容包括组装工艺路线,回流焊机的温度控制,焊膏印刷工艺(钢模板设计、钢模板开口设计、钢模板制作、焊膏材料选择),元器件贴装参数、焊接工艺技术、清洗工艺及质量检测(焊点形态检查——三维X光编程检测、测试焊点参数设置、检测结果统计)。

3 关键技术的攻关情况

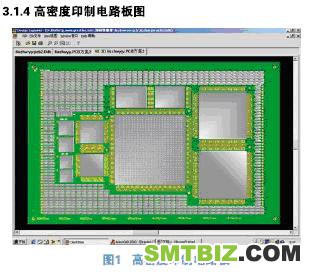

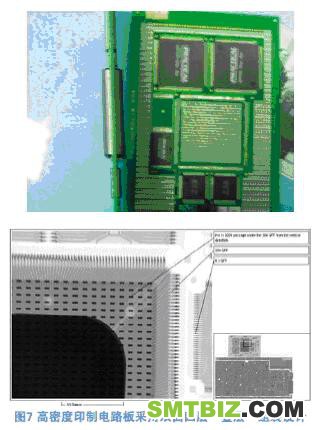

3.1 高密度印制电路板设计

设计高密度、高精度、细间距PCB板,构成双面四层“叠层”镜像组装模式。

PCB板A、B两面贴装高密度芯片(QFP、uBGA、CSP、TSOP、SOT、PQFP),然后在其四周贴装0402片式电阻、电容;并在PCB板A、B两面的304脚PQFP下面均贴装了0201片式元件。

组装模式应用双面四层“叠层”镜像组装设计和组装工艺技术。

高密度印制电路板的元件安装密度为31个/ cm2,焊点密度为94个/cm2。

3.1.1 高密度印制电路板的基本设计思路

典型的SMT设计流程主要包括总体设计、SMT电路设计、工艺设计、组装设计和检测设计。

高密度印制电路板设计预定的要求,主要用以进行现场实物演示、验收和技术指标测试验证,充分体现本课题全部技术指标;SMT设计流程图中所展示的各项流程,必须按程序进行。

包括:

(1)高密度印制电路板总体方案设计,即产品目标及经济分析,系统技术指标及功能分析;

(2)元器件和基板选择,建立试验用元器件数据库;

(3)元器件焊盘设计,建立元器件焊盘数据库;

(4)PCB布局及密度设计;

(5)组装方式和组装工艺方案设计;

(6)PCB的可制造性设计分析;

3.1.2 PCB总体设计

(1)基板

①耐热性——260℃,10秒

②铜箔的粘合强度——1.5Kg/cm2

③翘曲度——<0.0075mm/mm;即上翘曲<0.5mm,下翘曲<1.2mm

④结构及工艺

PCB为单层双面结构,厚度1.6mm

a)工艺夹持边5mm

b)定位孔为2+0.1mm(选1.2mm),精度±0.05mm;在定位孔周围1mm范围内不能有元件;以保证印制板能准确牢固地放置在表面安装设备的夹具上;

c)基准点的设计:

基准点的图形—■●▲+等;

基准点标记的直径—0.5~3mm,在同一印制板上基准点的尺寸变化不超过25um;

基准点周围的空旷区—基准点周围有等于3倍基准点半径的没有其它电路特性或标记的空旷区;基准点距离印制板边缘为3.0mm;

d)湿法阻焊膜及焊盘镀金工艺;

e)基板耐清洗:能在溶剂中浸5min,其表面不产生任何不良反映;

(2)元器件

见表1。

(3)布局:双面纯表面贴装

线宽/线距:0.1/0.2mm(针对QFP-168-0.3mm)

元器件之间焊盘边缘间距:0.5mm

焊点密度:50个/cm2

元器件密度:25只/cm2

细间距μBGA/CSP焊盘底部通孔技术(视制作能力);

焊盘尺寸视具体元器件封装及工艺而定。

元件距PCB边缘:大于5mm

(4)测试点:主要用于飞针在线测试;独立测试点(焊盘)直径大于0.2mm以上;

细间距μBGA/CSP引出测试线至测试端。测试点中心间距大于0.3mm。

(5)版图:正方形或长方形、双面板;整板定位点(圆形、直径1mm以下);

5mm及以下间距器件定位标记(圆形、直径1mm以下);

(6)设计方法:Protel 99;

标准封装直接采用软件自带焊盘图形库;自建焊盘图形库(依据所采用封装元器件指标);手工布局布线。符合高密度组装工艺要求。

设计高密度、高精度、细间距PCB板,构成双面四层“叠层”镜像组装模式。

PCB板A、B两面贴装高密度芯片(QFP、uBGA、CSP、TSOP、SOT、PQFP),然后在其四周贴装0402片式电阻、电容;并在PCB板A、B两面的304脚PQFP下面均贴装了0201片式元件。

组装模式应用双面四层“叠层”镜像组装设计和组装工艺技术。

高密度印制电路板的元件安装密度为31个/ cm2,焊点密度为94个/cm2。

3.1.1 高密度印制电路板的基本设计思路

典型的SMT设计流程主要包括总体设计、SMT电路设计、工艺设计、组装设计和检测设计。

高密度印制电路板设计预定的要求,主要用以进行现场实物演示、验收和技术指标测试验证,充分体现本课题全部技术指标;SMT设计流程图中所展示的各项流程,必须按程序进行。

包括:

(1)高密度印制电路板总体方案设计,即产品目标及经济分析,系统技术指标及功能分析;

(2)元器件和基板选择,建立试验用元器件数据库;

(3)元器件焊盘设计,建立元器件焊盘数据库;

(4)PCB布局及密度设计;

(5)组装方式和组装工艺方案设计;

(6)PCB的可制造性设计分析;

3.1.2 PCB总体设计

(1)基板

①耐热性——260℃,10秒

②铜箔的粘合强度——1.5Kg/cm2

③翘曲度——<0.0075mm/mm;即上翘曲<0.5mm,下翘曲<1.2mm

④结构及工艺

PCB为单层双面结构,厚度1.6mm

a)工艺夹持边5mm

b)定位孔为2+0.1mm(选1.2mm),精度±0.05mm;在定位孔周围1mm范围内不能有元件;以保证印制板能准确牢固地放置在表面安装设备的夹具上;

c)基准点的设计:

基准点的图形—■●▲+等;

基准点标记的直径—0.5~3mm,在同一印制板上基准点的尺寸变化不超过25um;

基准点周围的空旷区—基准点周围有等于3倍基准点半径的没有其它电路特性或标记的空旷区;基准点距离印制板边缘为3.0mm;

d)湿法阻焊膜及焊盘镀金工艺;

e)基板耐清洗:能在溶剂中浸5min,其表面不产生任何不良反映;

(2)元器件

见表1。

(3)布局:双面纯表面贴装

线宽/线距:0.1/0.2mm(针对QFP-168-0.3mm)

元器件之间焊盘边缘间距:0.5mm

焊点密度:50个/cm2

元器件密度:25只/cm2

细间距μBGA/CSP焊盘底部通孔技术(视制作能力);

焊盘尺寸视具体元器件封装及工艺而定。

元件距PCB边缘:大于5mm

(4)测试点:主要用于飞针在线测试;独立测试点(焊盘)直径大于0.2mm以上;

细间距μBGA/CSP引出测试线至测试端。测试点中心间距大于0.3mm。

(5)版图:正方形或长方形、双面板;整板定位点(圆形、直径1mm以下);

5mm及以下间距器件定位标记(圆形、直径1mm以下);

(6)设计方法:Protel 99;

标准封装直接采用软件自带焊盘图形库;自建焊盘图形库(依据所采用封装元器件指标);手工布局布线。符合高密度组装工艺要求。

3.1.3 元器件焊盘设计

SMC/SMD元器件焊盘设计原则:高密度印制电路板试验用SMD/SMC布局设计和焊盘图形设计是实施高密度印制电路板高密度、高精度设计的关键技术,是基于Web的eDFM电路设计的核心技术。元器件的焊盘不但要与元器件的尺寸相匹配,具有一定的兼容能力,同时要能适应各种不同加工工艺(如波峰焊和再流焊),最大程度地满足布局和布线的要求,并能适应从小批量到大批量生产和高质量组装的要求。高密度工艺样板由于选用高密度、细间距SMD/SMC,加工工艺只有再流焊焊接工艺能适应,焊盘图形设计时只考虑应用再流焊时的设计方案。

(1)高密度印制电路板试验用的片式元器件共有0201、0402chip、QFP、μBGA、CSP、TSOP 、PQFP等9种元器件,其封装形式不同,结构尺寸各异,在高密度PCB设计中焊盘的设计要求十分严格。

(2)在对试验用元器件和国内外现有的焊盘设计理论和数据进行长达半年调研的基础上,我们以元器件的尺寸为基本设计依据,考虑今后我们的产品主要应用于特殊的电子领域以及所选用的加工工艺和不同批量生产的要求,初步设计和建立了高密度印制电?钒迨匝橛玫钠?皆?骷?概掏夹巍>??啻涡拚??惴赫髑笾圃觳棵诺囊饧???泻概痰目芍圃煨苑治觯?购概躺杓仆季哂幸欢ǖ墓ひ招院蜕??浴?

(3)需要指出的是,虽然我们初步设计和建立了高密度印制电路板试验用的片式元器件焊盘图形,并将其应用于高密度印制电路板的设计,但建立通用焊盘数据库,进而进入网站尚须进行进一步试验和经过实践充分验证。

3.1.4 高密度印制电路板图

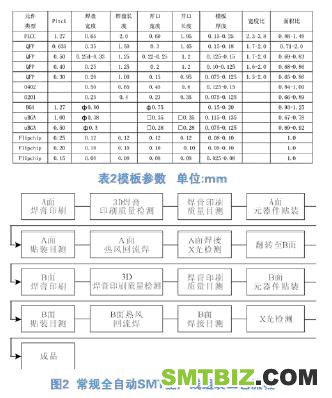

3.2 高密度印制电路板丝网漏板的设计和制作

高密度印制电路板设计和制作后,课题设计研究的重点攻关内容是高密度印制电路板丝网漏板的设计和制作;高密度印制电路板采用了0201元件和引脚中心距为0.3mm的QFP,对丝网漏板的设计和制作的要求极高,传统的激光刻蚀已不能满足高密度丝网漏板的加工要求;高密度丝网漏板设计和加工是一个带全局性的关键技术。

0201元件及引脚中心距为0.3mmQFP最佳加工方法是采用电铸法制造出0.08~0.10mm丝网模板,模板均匀度为3~5um/m2。其次是采用激光+电抛光,加工出厚度为0.1mm的丝网模板。

面积比=开口面积(LxW)/孔壁的面积〔2x(L+W)xT〕>0.66。(L为开口长度)

宽厚比(Aspect Ratio)=开口的宽度(W)/模板的厚度(T)>1.5。

模板参数见表2。

在完成高密度印制电路板丝网漏板设计的基础上,通过调研落实能保证含有0201元件和引脚中心距为0.3mm的QFP丝网漏板加工质量的协作单位,完成了高密度工艺样板的制作;高密度丝网模板选用激光+电抛光加工方法,丝网模板是厚度为0.1mm的不锈钢板。

3.3 高密度印制电路板组装工艺试验

根据已确定的合格的高密度印制电路板试验样板,完成高密度组装中特殊新型工艺的应用研究,进一步完善高密度设计要求、高密度组装工艺方案的可靠性,为后期型号产品的高密度组装应用的一次成功率的可能性确立坚实的基础!

针对高密度印制电路板组装技术上的难度,以《高密度印制电路板组装工艺试验方案》为技术依据,以高密度印制电路板为试验对象,制定组装工艺试验实施方案;关键工艺的实现以国内先进组装技术、设备为依托进行高密度印制电路板组装工艺试验为第一方案,以手动或半自动SMT组装生产线的工艺装备、技术资源为依托进行高密度印制电路板组装工艺试验为备份方案;通过试验初步了解和掌握高密度印制电路板在具有国际先进技术水平的全自动SMT生产线的组装工艺技术。

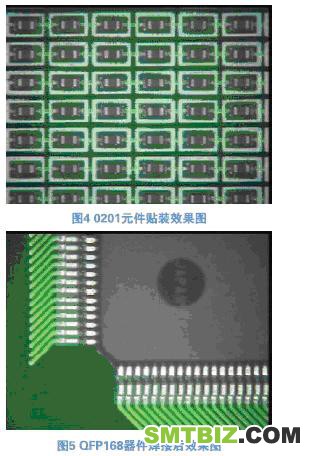

1)组装工艺流程

(1)全自动SMT生产线组装工艺流程

(2)试验分析

在完成组装试验前的技术准备工作条件下,具体试验过程中0201及引脚中心距0.3mmQFP的组装焊接都不构成试验的关键技术;高密度印制电路板组装试验的关键技术是能否把双面四层元器件,即A、B两面的0201元件及304脚QFP器件分别能一次焊好;如能一次焊好,这是最理想的。第一块工艺样板板A面焊接后用X光检测,如发现0201元件及304脚QFP器件不能同时焊好,采用特殊SMT工艺流程。

2)关键组装工艺技术

(1)温度阶梯焊工艺

由于PCB板A、B两面贴装高密度芯片(QFP、uBGA、CSP、TSOP、SOT、PQFP),然后在其四周贴装0402片式电阻、电容;并在PCB板A、B两面的304脚PQFP下面均贴装了0201片式电阻、电容。则在焊接工艺中拟采取温度阶梯焊工艺。即对PCB的A面元器件应用无铅焊料,而对PCB的B面元器件应用Sn/Pb焊料;对PQFP采用低温焊料。

(2)焊膏丝印工艺技术

由于PCB的A、B两面的304脚QFP的下面均贴装了805个0201元件,304脚QFP与0201元件之间的距离只不到0.1mm,除了必须严格控制丝网模板的厚度、均匀度外,还必须严格控制刮刀速度、刮刀压力和离板速度,保证焊膏的均匀度。

3)高密度印制电路板组装工艺试验步骤

(1)焊膏印刷试验:

用1块高密度印制电路板进行丝网模板与印制板的对位、焊膏印刷试验;调节各项印刷参数。

(2)组装工艺全过程试验

用1块高密度印制电路板进行从丝印、贴片、焊接的组装工艺全过程试验,调整回流焊温度曲线,重点检测双面四层0201元件及304脚QFP器件的焊接质量;

(3)进行组装工艺试验,调整修改各项工艺参数;

(4)高密度印制电路板组装工艺验证

用1块高密度印制电路板进行从丝印、贴片、焊接的组装工艺全过程试验,调整回流焊温度曲线,重点检测双面四层0201元件及304脚QFP器件的焊接质量;

(3)进行组装工艺试验,调整修改各项工艺参数;

(4)高密度印制电路板组装工艺验证

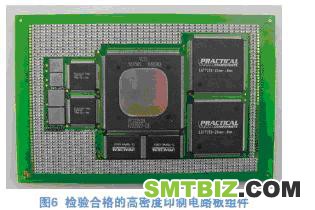

4 结束语

超小型0201和0402chip及细间距QFP、CSP和uBGA的应用,使组装密度达到高密度、高精度的目的,在通讯设备及计算机中今后大量应用的是双面(或多层)PCB高密度“叠层”组装技术,可以认为,双面(或多层)PCB高密度“叠层”组装技术是一种有着广泛应用前景的电子组装技术。

目前,高密度组装的设计思维已融入型号产品PCB的系统设计中,该项成果的推广应用将使我国电子装备中电路模块的面积在原有的基础上缩小1/3,重量减轻1/3,电路模块功能进一步扩展,促进和推动我国军事电子装备的板级电路组装上水平。

除此以外,该项目工艺技术研究内容通用性范围极大,技术覆盖面涉及所有板级电路的电子产品,技术应用具备极广,尤其在高密度板级电路的可制造性设计、可测试性设计研究及实施应用等方面创立一个新途径,力争?谙低承PCB设计的项目和流程管理上有所建树。

超小型0201和0402chip及细间距QFP、CSP和uBGA的应用,使组装密度达到高密度、高精度的目的,在通讯设备及计算机中今后大量应用的是双面(或多层)PCB高密度“叠层”组装技术,可以认为,双面(或多层)PCB高密度“叠层”组装技术是一种有着广泛应用前景的电子组装技术。

目前,高密度组装的设计思维已融入型号产品PCB的系统设计中,该项成果的推广应用将使我国电子装备中电路模块的面积在原有的基础上缩小1/3,重量减轻1/3,电路模块功能进一步扩展,促进和推动我国军事电子装备的板级电路组装上水平。

除此以外,该项目工艺技术研究内容通用性范围极大,技术覆盖面涉及所有板级电路的电子产品,技术应用具备极广,尤其在高密度板级电路的可制造性设计、可测试性设计研究及实施应用等方面创立一个新途径,力争?谙低承PCB设计的项目和流程管理上有所建树。

项目技术指标在国内处于领先地位,相当于国际上90年代末SMT技术水平,基本上是中视频频段和小功率范围,没有涉及微波、毫米波频段及大功率范围。微波、毫米波频段及大功率范围的板级电路高密度、?呔?茸樽凹际醣亟?俏颐窍乱徊街氐愕墓ス啬谌荨?

我们2002年在《板级电路高密度、高精度组装技术》试验中所采取的“叠层”组装设计和工艺技术,就是近几年在全球掀起的元器件堆叠装配(POP,Package on Package)技术。

元器件堆叠装配(POP,Package on Package)技术的出现,进一步模糊了一级封装与二级组装之间的界线,在大大提高逻辑运算功能和存储空间的同时,也为用户提供了元器件组合装配的可能,生产成本得以更有效的控制,由此,元器件堆叠装配是一种值得考虑的优选方案;毫无疑问,随着元器件小型化高密度封装的发展,对于高速与高精度装配的要求将变得更加关键,相关的组装设备和工艺技术也更具先进性与高灵活性,元器件堆叠装配(POP,Package on Package)技术必将经受这一新的挑战。