藉由 PCB 分层堆栈设计控制 EMI 辐射

PCB 分层堆栈在控制 EMI 辐射中的作用和设计技巧。

By 张兴隆

解决 EMI 问题的办法很多,现代的 EMI 抑制方法包括:利用 EMI 抑制涂层、选用合适的 EMI 抑制零配件和 EMI 仿真设计等。本文从最基本的 PCB 布板出发,讨论 PCB 分层堆栈在控制 EMI 辐射中的作用和设计技巧。

电源总线

在 IC 的电源引脚附近合理地安置适当容量的电容,可使 IC 输出电压的跳变来得更快。然而,问题并非到此为止。由于电容呈有限频率响应的特性,这使得电容无法在全频带上生成干净地驱动 IC 输出所需要的谐波功率。除此之外,电源总线上形成的瞬态电压在去耦路径的电感两端会形成电压降,这些瞬态电压就是主要的共模 EMI 干扰源。我们应该怎么解决这些问题?

就我们电路板上的 IC 而言, IC 周围的电源层可以看成是优良的高频电容器,它可以收集为干净输出提供高频能量的分立电容器所泄漏的那部份能量。此外,优良的电源层的电感要小,从而电感所合成的瞬态信号也小,进而降低共模 EMI 。

当然,电源层到 IC 电源引脚的联机必须尽可能短,因为数字信号的上升沿越来越快,最好是直接连到 IC 电源引脚所在的焊盘上,这要另外讨论。

为了控制共模 EMI ,电源层要有助于去耦和具有足够低的电感,这个电源层必须是一个设计相当好的电源层的配对。有人可能会问,好到什么程度才算好?问题的答案取决于电源的分层、层间的材料以及工作频率 ( 即 IC 上升时间的函数 ) 。通常,电源分层的间距是 6mil ,夹层是 FR4 材料,则每平方英寸电源层的等效电容约为 75pF 。显然,层间距越小电容越大。

上升时间为 100 到 300ps 的器件并不多,但是按照目前 IC 的发展速度,上升时间在 100 到 300ps 范围的器件将占有很高的比例。对于 100 到 300ps 上升时间的电路, 3mil 层间距对大多数应用将不再适用。那时,有必要采用层间距小于 1mil 的分层技术,并用介电常数很高的材料代替 FR4 介电材料。现在,陶瓷和加陶塑料可以满足 100 到 300ps 上升时间电路的设计要求。

尽管未来可能会采用新材料和新方法,但对于今天常见的 1 到 3ns 上升时间电路、 3 到 6mil 层间距和 FR4 介电材料,通常足够处理高端谐波并使瞬态信号足够低,就是说,共模 EMI 可以降得很低。本文给出的 PCB 分层堆栈设计实例将假定层间距为 3 到 6mil 。

电磁屏蔽

从信号走线来看,好的分层策略应该是把所有的信号走线放在一层或若干层,这些层紧挨着电源层或接地层。对于电源,好的分层策略应该是电源层与接地层相邻,且电源层与接地层的距离尽可能小,这就是我们所讲的“分层”策略。

PCB 堆栈

什么样的堆栈策略有助于屏蔽和抑制 EMI ?以下分层堆栈方案假定电源电流在单一层上流动,单电压或多电压分布在同一层的不同部份。多电源层的情形稍后讨论。

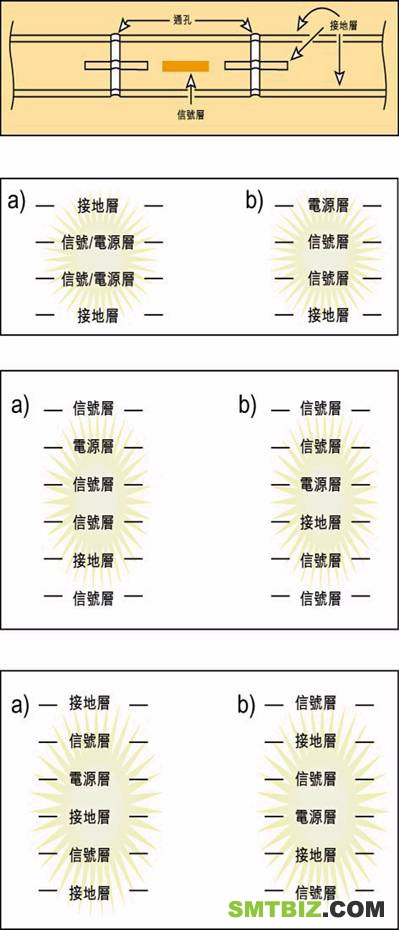

4 层板

4 层板设计存在若干潜在问题。首先,传统的厚度为 62mil 的四层板,即使信号层在外层,电源和接地层在内层,电源层与接地层的间距仍然过大。

如果成本要求是第一位的,可以考虑以下两种传统 4 层板的替代方案。这两个方案都能改善 EMI 抑制的性能,但只适用于板上组件密度足够低和组件周围有足够面积 ( 放置所要求的电源覆铜层 ) 的场合。

第一种为首选方案, PCB 的外层均为地层,中间两层均为信号 / 电源层。信号层上的电源用宽线走线,这可使电源电流的路径阻抗低,且信号微带路径的阻抗也低。从 EMI 控制的角度看,这是现有的最佳 4 层 PCB 结构。第二种方案的外层走电源和地,中间两层走信号。该方案相对传统 4 层板来说,改进要小一些,层间阻抗和传统的 4 层板一样欠佳。

如果要控制走线阻抗,上述堆栈方案都要非常小心地将走线布置在电源和接地铺铜岛的下边。另外,电源或地层上的铺铜岛之间应尽可能地互连在一起,以确保 DC 和低频的连接性。

6 层板

如果 4 层板上的组件密度比较大,则最好采用 6 层板。但是, 6 层板设计中某些迭层方案对电磁场的屏蔽作用不够好,对电源总线瞬态信号的降低作用甚微。下面讨论两个实例。

第一例将电源和地分别放在第 2 和第 5 层,由于电源覆铜阻抗高,对控制共模 EMI 辐射非常不利。不过,从信号的阻抗控制观点来看,这一方法却是非常正确的。

第二例将电源和地分别放在第 3 和第 4 层,这一设计解决了电源覆铜阻抗问题,由于第 1 层和第 6 层的电磁屏蔽性能差,差模 EMI 增加了。如果两个外层上的信号线数量最少,走线长度很短 ( 短于信号最高谐波波长的 1/20) ,则这种设计可以解决差模 EMI 问题。将外层上的无组件和无走线区域铺铜填充并将覆铜区接地 ( 每 1/20 波长为间隔 ) ,则对差模 EMI 的抑制特别好。如前所述,要将铺铜区与内部接地层多点相联。

通用高性能 6 层板设计一般将第 1 和第 6 层布为地层,第 3 和第 4 层走电源和地。由于在电源层和接地层之间是两层居中的双微带信号线层,因而 EMI 抑制能力是优异的。该设计的缺点在于走线层只有两层。前面介绍过,如果外层走线短且在无走线区域铺铜,则用传统的 6 层板也可以实现相同的堆栈。

另一种 6 层板布局为信号、地、信号、电源、地、信号,这可实现高级信号完整性设计所需要的环境。信号层与接地层相邻,电源层和接地层配对。显然,不足之处是层的堆栈不平衡。

这通常会给加工制造带来麻烦。解决问题的办法是将第 3 层所有的空白区域填铜,填铜后如果第 3 层的覆铜密度接近于电源层或接地层,这块板可以不严格地算作是结构平衡的电路板。填铜区必须接电源或接地。连接过孔之间的距离仍然是 1/20 波长,不见得处处都要连接,但理想情况下应该连接。

10 层板

由于多层板之间的绝缘隔离层非常薄,所以 10 或 12 层的电路板层与层之间的阻抗非常低,只要分层和堆栈不出问题,完全可望得到优异的信号完整性。要按 62mil 厚度加工制造 12 层板,困难比较多,能够加工 12 层板的制造商也不多。

由于信号层和回路层之间总是隔有绝缘层,在 10 层板设计中分配中间 6 层来走信号线的方案并非最佳。另外,让信号层与回路层相邻很重要,即板布局为信号、地、信号、信号、电源、地、信号、信号、地、信号。

这一设计为信号电流及其回路电流提供了良好的通路。恰当的布线策略是,第 1 层沿 X 方向走线,第 3 层沿 Y 方向走线,第 4 层沿 X 方向走线,以此类推。直观地看走线,第 1 层 1 和第 3 层是一对分层组合,第 4 层和第 7 层是一对分层组合,第 8 层和第 10 层是最后一对分层组合。当需要改变走线方向时,第 1 层上的信号线应藉由“过孔”到第 3 层以后再改变方向。实际上,也许并不总能这样做,但作为设计概念还是要尽量遵守。

同样,当信号的走线方向变化时,应该藉由过孔从第 8 层和第 10 层或从第 4 层到第 7 层。这样布线可确保信号的前向通路和回路之间的耦合最紧。例如,如果信号在第 1 层上走线,回路在第 2 层且只在第 2 层上走线,那么第 1 层上的信号即使是藉由“过孔”转到了第 3 层上,其回路仍在第 2 层,从而保持低电感、大电容的特性以及良好的电磁屏蔽性能。

如果实际走线不是这样,怎么办?比如第 1 层上的信号线经由过孔到第 10 层,这时回路信号只好从第 9 层寻找接地平面,回路电流要找到最近的接地过孔 ( 如电阻或电容等组件的接地引脚 ) 。如果碰巧附近存在这样的过孔,则真的走运。假如没有这样近的过孔可用,电感就会变大,电容要减小, EMI 一定会增加。

当信号线必须经由过孔离开现在的一对布线层到其它布线层时,应就近在过孔旁放置接地过孔,这样可以使回路信号顺利返回恰当的接地层。对于第 4 层和第 7 层分层组合,信号回路将从电源层或接地层 ( 即第 5 层或第 6 层 ) 返回,因为电源层和接地层之间的电容耦合良好,信号容易传输。

多电源层的设计

如果同一电压源的两个电源层需要输出大电流,则电路板应布成两组电源层和接地层。在这种情况下,每对电源层和接地层之间都放置了绝缘层。这样就得到我们期望的等分电流的两对阻抗相等的电源总线。如果电源层的堆栈造成阻抗不相等,则分流就不均匀,瞬态电压将大得多,并且 EMI 会急剧增加。

如果电路板上存在多个数值不同的电源电压,则相应地需要多个电源层,要牢记为不同的电源创建各自配对的电源层和接地层。在上述两种情况下,确定配对电源层和接地层在电路板的位置时,切记制造商对平衡结构的要求。

总结

鉴于大多数工程师设计的电路板是厚度 62mil 、不带盲孔或埋孔的传统印制电路板,本文关于电路板分层和堆栈的讨论都局限于此。厚度差别太大的电路板,本文推荐的分层方案可能不理想。此外,带盲孔或埋孔的电路板的加工制程不同,本文的分层方法也不适用。

电路板设计中厚度、过孔制程和电路板的层数不是解决问题的关键,优良的分层堆栈是保证电源总线的旁路和去耦、使电源层或接地层上的瞬态电压最小并将信号和电源的电磁场屏蔽起来的关键。理想情况下,信号走线层与其回路接地层之间应该有一个绝缘隔离层,配对的层间距 ( 或一对以上 ) 应该越小越好。根据这些基本概念和原则,才能设计出总能达到设计要求的电路板。现在, IC 的上升时间已经很短并将更短,本文讨论的技术对解决 EMI 屏蔽问题是必不可少的。

Rick Hartley 是高速通讯设备制造商 Applied Innovation 公司的高级硬件工程师,他在电子设计领域有 35 年经验,最近 25 年他专注于印刷电路板设计和开发,过去 10 年他领导高速数字和 RF 电路板设计,重点是 EMI 控制。感兴趣的读者可以藉由电子邮件: rickh@aiinet.com 与作者联系。