底部填充倒装芯片提高热机可靠性

由于芯片和封装管脚数目增加的速度较管脚成本下降的速度更快,业界需要价格适中的组装和封装新技术。今天,与 QFP 和 SO 封装器件相比,采用先进和复杂技术生产的组件数量仍然很少。根据 Dataquest 的统计, QFP 和 SO 封装几乎占了集体电路 (IC) 封装市场的 80% 。然而,这两种封装都只适于低管脚数的应用。

目前,芯片和封装之间的相互连接大多仍采用邦定方法。不久的将来将必须采用细线互连技术,以满足新的高端产品应用需求。实现它的一种方法是采用倒装芯片技术。

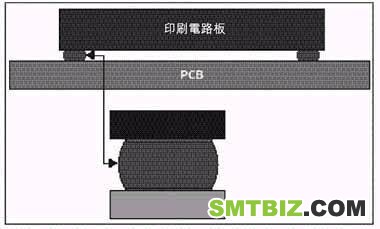

倒装芯片是一种直接芯片贴装 (direct-chip-attach) 技术。先在裸片底部制作出很小的焊接用凸起数组,其直径通常为 50 到 125 酸,然后将裸片倒转贴在基片上 ( 图 1) 。

图 1 :贴装在 PCB 上的倒装芯片裸片。

与其它芯片互连技术相比,倒装芯片贴装技术有很多优点:它减小了信号传播延迟,因而具有较好的电气性能;尺寸相对较小,而封装密度较高,因此每平方厘米的整合度更高。其它优点还包括:更小的组装容差,在回流过程中具有较高的自我校准能力,易于修补,以及散热能力增强。

热疲劳故障

一般来说,在倒装芯片组装中采用焊接连接,其热机械性能会较差。硅片和基片之间热膨胀系数的差异,导致了焊点上产生较大的塑性张力。

然而,藉由在芯片和基片之间的空隙中填充环氧树脂材料,可以获得较高的可靠性。如果不采用这种底部填充方法,故障率为 50% 的热循环的次数甚至会低于 200 。

若精心选择底部填充材料,就有可能将热疲劳可靠性提高 10 倍以上。对底部填充材料和空隙形状的深入了解,还可使性能进一步提高。

利用热疲劳的实验分析,可以将每个设计实现为样机,从而优化倒装芯片设计。然后对样机进行热循环次数测试。在对设计进行修正以后,仍要采用相同的步骤 ( 制造样机和进行测试 ) 。但这种方法既耗时又费钱。而且采用这种方法,人们对故障机理的了解也很有限。

比较起来,在设计步骤之后和制造样机之前,可以采用建模分析技术。这有助于减少花费在实验上的时间和资金,并能对故障机理有更深入的了解,同时还可以藉由参数模拟来优化整个过程。

IMEC 公司先进封装技术部门的一个研究开发 (R&D) 小组对底部填充和底部填充组装进行了分析。用一个非线性二维有限元模型来计算焊点上的塑性变形。同时,用一个采纳 Coffin-Manson 关系式的热疲劳寿命模型将这些变形转换为热循环次数的估计值。再用以前的实验结果来确认该模型。

在采用底部填充材料和不采用底部填充材料的情况下,分别完成倒装芯片的组装。为一个厚 0.6mm 、面积为 10mm 2 、焊点高度为 75 酸的裸片建立一个二维有限元分析模型。该裸片是贴装在一个 1.2mm 厚的 FR4 PCB 上的倒装芯片。这一测试使研究开发 (R&D) 小组得出了本文中的结论。

非底部填充组装

这种情况下,焊点的剪切变形处于支配地位,这是由芯片和基片之间的水平位移差造成的。预期的故障率为 50% 的热循环 (- 55 ℃ 到 125 ℃ ) 次数较低,为 200 次。在模型中,增加芯片的尺寸将使热疲劳寿命以对数率降低。此外,降低焊点高度也将使 50% 故障率时的热循环次数 N50% 以相同的方式减小。另一方面,可以藉由将焊点变凹的方法,使热循环次数提高到 600 。

与其它芯片互连技术相比,倒装芯片贴装技术有很多优点:它减小了信号传播延迟,因而具有较好的电气性能;尺寸相对较小,而封装密度较高,因此每平方厘米的整合度更高。其它优点还包括:更小的组装容差,在回流过程中具有较高的自我校准能力,易于修补,以及散热能力增强。

热疲劳故障

一般来说,在倒装芯片组装中采用焊接连接,其热机械性能会较差。硅片和基片之间热膨胀系数的差异,导致了焊点上产生较大的塑性张力。

然而,藉由在芯片和基片之间的空隙中填充环氧树脂材料,可以获得较高的可靠性。如果不采用这种底部填充方法,故障率为 50% 的热循环的次数甚至会低于 200 。

若精心选择底部填充材料,就有可能将热疲劳可靠性提高 10 倍以上。对底部填充材料和空隙形状的深入了解,还可使性能进一步提高。

利用热疲劳的实验分析,可以将每个设计实现为样机,从而优化倒装芯片设计。然后对样机进行热循环次数测试。在对设计进行修正以后,仍要采用相同的步骤 ( 制造样机和进行测试 ) 。但这种方法既耗时又费钱。而且采用这种方法,人们对故障机理的了解也很有限。

比较起来,在设计步骤之后和制造样机之前,可以采用建模分析技术。这有助于减少花费在实验上的时间和资金,并能对故障机理有更深入的了解,同时还可以藉由参数模拟来优化整个过程。

IMEC 公司先进封装技术部门的一个研究开发 (R&D) 小组对底部填充和底部填充组装进行了分析。用一个非线性二维有限元模型来计算焊点上的塑性变形。同时,用一个采纳 Coffin-Manson 关系式的热疲劳寿命模型将这些变形转换为热循环次数的估计值。再用以前的实验结果来确认该模型。

在采用底部填充材料和不采用底部填充材料的情况下,分别完成倒装芯片的组装。为一个厚 0.6mm 、面积为 10mm 2 、焊点高度为 75 酸的裸片建立一个二维有限元分析模型。该裸片是贴装在一个 1.2mm 厚的 FR4 PCB 上的倒装芯片。这一测试使研究开发 (R&D) 小组得出了本文中的结论。

非底部填充组装

这种情况下,焊点的剪切变形处于支配地位,这是由芯片和基片之间的水平位移差造成的。预期的故障率为 50% 的热循环 (- 55 ℃ 到 125 ℃ ) 次数较低,为 200 次。在模型中,增加芯片的尺寸将使热疲劳寿命以对数率降低。此外,降低焊点高度也将使 50% 故障率时的热循环次数 N50% 以相同的方式减小。另一方面,可以藉由将焊点变凹的方法,使热循环次数提高到 600 。

硅片和基片材料之间热膨胀系数 (CTE) 的差别也决定了剪切变形的程度。所以,正确选择基片材料非常重要。研究人员发现,使用 CTE 值为 5.6ppm/0K 的氧化铝作为基片材料,能导致 N50%=600, 是 CTE 值为 15ppm/0K 的 FR4 的 4 倍。

底部填充的倒装芯片

对芯片和基片之间的空隙进行底部填充可增加可靠性。焊点的塑性变形非常复杂。在热机械分析模型中,底部填充倒装芯片组件像一个由三种材料形成的结构。选择匹配性能好的底部填充材料是重要的一环。它由 CTE 和 Young 的弹性系数 (E) 决定。

一般地,在底部填充倒装芯片的焊接处,可产生三种不同的塑性张力模式。首先是剪切塑性张力,它是由芯片和基片之间水平位移的不匹配引起的。然后是水平法线 (normal) 塑性张力,由底部填充材料固有的水平法线张力引起。第三种是由于底部填充材料的垂直变形不匹配而造成的垂直法线塑性张力。

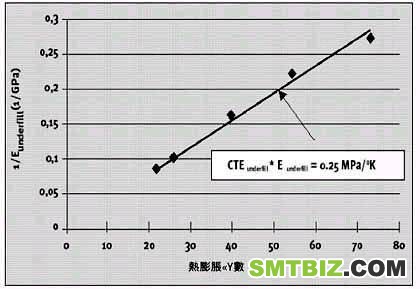

根据模型计算的结果,研究开发小组得出下面的结论:两个材料参数, CTE 和 E ,对倒装芯片组件的热疲劳可靠性都有较大的影响。底部填充材料的硬度愈大,热疲劳寿命愈长。此外,存在一个依赖于弹性系数的最优热膨胀系数 ( 图 2) 。

图 2 :底部填充材料的 E 值和 CTE 值 ( 实线 ) 之间具有相关性:两个参数的乘积是常数,为 0.25MPa/°K 。

与非底部填充倒装芯片组装相比 ( N 50% 大约为 200) 相比,在底部填充倒装芯片组装中,如果底部填充材料的弹性系数大于 10Gpa , CTE=25ppm/0K ,就可获得N 50% 高于 15,000 的热疲劳寿命。

最后,研究人员检验了不同的基片材料,如 A12O3 、聚合物和硅。在所有情形下,底部填充均能增加对热疲劳的抵抗性。

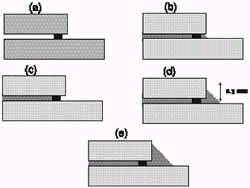

在裸片边缘进行底部填充

IMAC 小组还研究了填角的各种不同情况 ( 图 3) 。如果填料未能充分包围焊点,其可靠性仍然较差;如果填料发配了裸片侧面的大约一半,就可以得到比原来高 500 倍的最优值;如果裸片发配过度,硅片和填料之间的垂直热变形就会很不匹配,使芯片和焊点上产生周而复始的推力和拉力,显著地减小了可靠性。

图 3 :裸片边缘有不同填角:从无底层填料 (a) 到裸片侧面完全发配 (e) 。

影响可靠性的其它参数包括焊盘离芯片边缘的距离和芯片的尺寸。距裸片边缘越远,可靠性愈好。

区域数组和周边数组

可以藉由增大距裸片边缘的距离来提高可靠性。这对于封装类型是选择区域数组还是周边数组,有较大的影响。典型地,对于一个 10× 10mm 的倒装芯片,如果它贴装在 FR4 PCB 上,并使用 E=10Gpa 、 CTE=25ppm/0K 的底层填料,那么,采用区域数组封装的可靠性是采用周边数组封装的六倍。

如果数组外部的焊点远离裸片边缘,则焊点上几乎不会产生塑性张力,因此可获得较高的热可靠性。

由以上的结果可知,仔细选择倒装芯片的封装设计,能够显著地增加热可靠性。总的来说,倒装芯片组件的热疲劳可靠性较低。藉由对倒装芯片组件进行底部填充,热疲劳寿命可以增加至少 10 倍。

如果使用具有高弹性系数 ( 即刚性的 ) 和低热膨胀系数的填料,还可进一步优化。藉由发配裸片的半个侧面,可以获得更好的效果。

所以,区域数组封装可能是下一代高管脚数芯片封装的唯一选择。在倒装芯片相互连接的情形下 , 这些封装比周边数组封装具有更高的热疲劳寿命。

图 -BOX :具有 10,000 个逻辑电路的 ASIC 需要大约 300 个管脚;但具有 100,000 个电路的芯片只需要 1,000 多个管脚。

细线互连 (fine-line interconnections)

1997 SIA 规划 (roadmap) 表明,在下一个十年内,电子设备的内部连接将发生显著变化。人们期望,芯片内部连接的间距 ( 相邻两个管脚的距离 ) 随芯片特征尺寸的减小而减小。这意味着 0.25 酸的 IC 特征尺寸要求 250 酸的间距, 0.18 酸尺寸要求 180 酸的间距,等等。

DRAM 和 SRAM 只需较少数量的 I/O 管脚 ( 少于 64 个 ) ,就可满足每个芯片的较大位数 (64Mb 或更多 ) 。然而, ASIC 的管脚数随着每个组件中逻辑电路数目的增加而迅速增加。它服从 Rent 定律。该定律表明,在 ASIC 逻辑电路数的对数和封装上 I/O 管脚数的对数之间存在着线性关系。

高端微处理器现已达到创记录的 1GHz 的高频率。这里的问题不是管脚数目,而是 I/O 终端的电气特性。更短、更直接的连接具有更好的性能,它能使芯片之间的信号传播延迟减至最小。