倒装芯片:向主流制造工艺推进

By Dr. Scott Joslin, James Lance, Daniel Yeaple and Douglas Hendricks

创新的制造与设计技术使得成百万使用倒装芯片装配的寻呼机成功地制造出来。

对较小外形和较多功能的低成本电子设备的需求继续在增长。这些快速变化的市场挑战着电子制造商,降低制造成本以保证可接受的利润率。倒装芯片装配 (flip chip assembly) 被认为是推进低成本、高密度携带型电子设备的制造所必须的一项技术。

在低成本应用中,倒装芯片的成功是因为它可达到相对于传统表面贴装组件包装更大的成本效益。例如,一款新的寻呼机利用了倒装芯片技术将微控制器装配于 PCB ,因为倒装芯片使用较少的电路板空间,比传统的塑料球栅数组 (PBGA, plastic ball grid array) 成本较低。

材料

集成电路 (Integraded circuit)

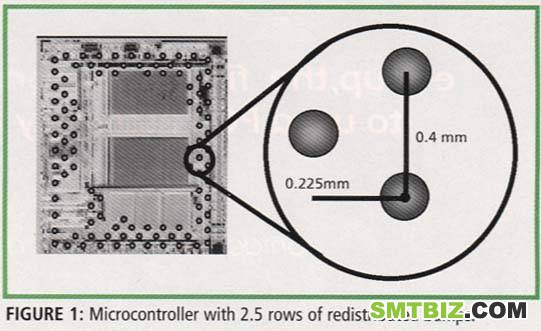

在这款寻呼机中的集成电路 (IC, integrated circuit) 是一个 5 x 5.6 mm 的微控制器,要求 100 个输入 / 输出 (I/O) 连接于 PCB 。将四周 I/O 重新分配为 2.5 排减少点数 (depopulated) 的球栅数组形式来接纳 PCB 的线 / 空格以及通路孔焊盘的限制。锡球 (bump) 布局与间距如图一所示。

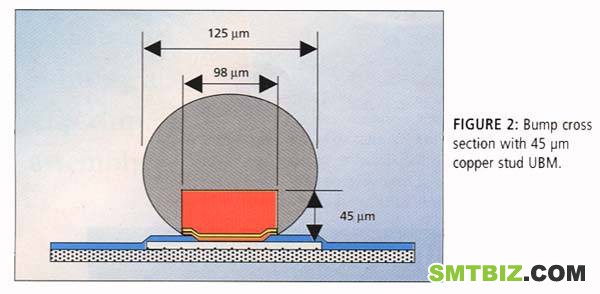

使用了电镀共晶锡 / 铅锡球,因为与其它的替代者比较,它的成本低得多。锡球的直径大约为 125 µ m ,球下金属 (UBM, under bump metalization) 为一个顾客要求的 45 µ m 的铜柱,如图二。

印刷电路板 (PCB, printed circuit board)

成本因素决定这款寻呼机的 PCB 的布局。 PCB 是标准的 FR-4 ,四个金属层和一个无电镀镍 / 金表面涂层。由于增加材料成本和有限的可获得性,所以没有使用高密度互连 (HDI, high-density interconnect) 技术。无电镀镍 / 金表面涂层满足所有产品的要求。现场可靠性问题排除了选择有机可焊性保护层 (OSP, organic solderability preservative) ,选择性镍 - 金的成本增加也没有吸引性。

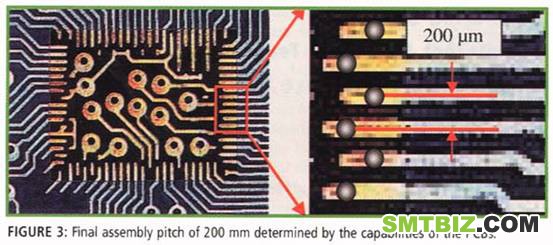

最低成本的 PCB 供货商的工艺能力限制板的密度为 100 µ m 线 / 空和 0.5mm 的通路孔焊盘。因此,所有通路孔 (via) 都是通孔 (through-hole) 型,避免盲孔 (blind via) 的成本增加。这些限制和阻焊层公差决定 IC 的分布形式、锡球尺寸和装配间距,并定义芯片贴放要求。

限制通路孔的焊盘尺寸为最小的 0.5mm ,意味着芯片 (die) 底下只能放 13 个通路孔 (via) 剩下的 I/O 不得不用 100 µ m 的线与空在基板顶面走出去。只使用定面金属层来布线剩下的 87 个 I/O ,这给 IC 的重新分布形式定下了一个标准。 100 µ m 线与空的设计要求将最终装配间距固定在 200 µ m( 图三 ) 。

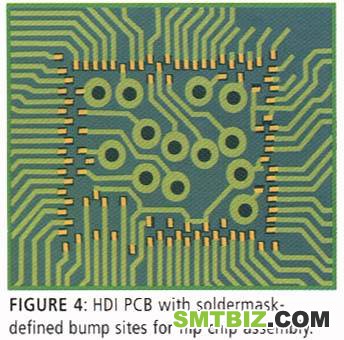

阻焊层 (soldermask) 的设计与工艺限制对直接芯片安装 (DCA, direct chip attachment) 的装配过程是关键的。必须控制电镀共晶锡球的熔湿 (wet) ,以防止回流期间焊接点的完全倒塌和断源。 阻焊层可用来限制焊锡熔湿和控制锡球塌落的程度。这个控制是通过为每个锡球座设计离散的阻焊层开口来完成的 ( 图四 ) 。在本文所述的应用中,工艺的限制和贴装设备的能力使得不能使用单独定义的锡球座。

低成本 PCB 供货商通常只可以维持大批量生产时的± 75 µ m 阻焊层对位精度。用于芯片贴装 (die placement) 的导向丝杆设备的精度能力为± 50 µ m 。这些公差的累积要求 0.375mm 的阻焊层开口来保证贴装与回流过程达到 6 σ 能力。这个尺寸的开口容纳阻焊层的偏移和贴装公差,而不会将 120 µ m 直径的锡球放到阻焊层上。[pagebeak]

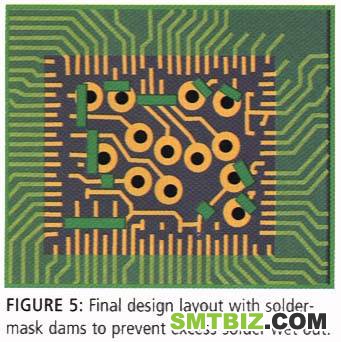

最后布局利用单个的阻焊条或“堤挡”来限制焊锡熔湿流出,并在关键区域防止断源。堤挡放在流道上,直接连接于内通孔的联机孔 (via) 或那些认为太长的在线。要求总共 11 条阻焊堤挡或条来足够地保护装配 ( 图五 ) 。这随机放置的阻焊条提供整个芯片的连续的毛细管作用,结果得到均匀的充胶 (underfill) 流峰,和无空洞的密封胶。

锡球 (solder bump)

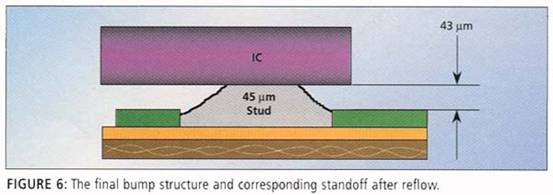

在阻焊层可用于控制低成本、密间距应用的芯片 (die) 塌落之前,必须改进材料的定位和孔的准确度。阻焊堤挡可有效的防止焊锡点断源,但不能充分地限制回流时的锡球倒塌 (die collapse) 。为了有效地控制芯片离板高度,锡球的铜 UBM( 锡球下的金属 ) 需要改进。使用 45 µ m 的铜柱 UBM 可达到连续一致的工艺过程和可靠性。这个锡球结构提供阻焊层之上 43 µ m 的间隙,容易作底部充胶。图六显示最后的锡球结构和回流之后相应的力板高度。

工艺过程

建立最终的设计版本和材料规格,允许制造过程得到优化,达到最大的产量与最好的质量。虽然与标准的表面贴装相似,倒装芯片要求特殊的考虑因素。在工厂实施之前的准备将改进生产线产量,过程合格率和产品可靠性。倒装芯片工艺包括上助焊剂 (fluxing) 、芯片贴装 (die placement) 、回流 (reflow) 、底部充胶 (underfill) 和固化 (cure) 。

上助焊剂 (fluxing)

上助焊剂 (fluxing) 是倒装芯片工艺的第一步,其重要性经常被低估了。在形成连接之前,助焊剂将芯片保持在位置上,减少氧化和加速共晶焊锡球的回流。本应用中使用的免洗助焊剂具有高粘着性 (tack) 、低粘度 (viscosity) 、长蒸发时间、最低回流焊后残留物、低毒性和最小气味。

在锡球回流之前芯片的移动是一个关注,因为 200 µ m 的装配间距几乎不允许有对位错误。造成未对准或相对移位元芯片的原因可能不同,但包括:

- PCB 弯曲变形 (warped PCB) :当芯片 (die) 贴放到电路板表面时,弯曲的板可能会柔曲。已经贴装在板上的芯片,在剩下的芯片贴装时,要经受电路板的类似于崩床的运动。

- 板的传送:在芯片 (die) 贴装之后,装配传送到回流焊炉必须流畅。传送带对不准或贴装单元的升起定位机构或传送带的突然加速都可能造成芯片移位元。

- 炉的情况:炉内高速气流将吹动芯片偏移定位。

具有高粘着性和低蒸发速率的助焊剂系统将减少这些材料处理的缺陷和提高更快的生产线速度。如果助焊剂在芯片贴装或回流之前蒸发,那么 IC 更可能移位。慢的蒸发保持最多的助焊剂,在回流炉的升温和保温区期间,把芯片固定在位。理想的,助焊剂不应该蒸发太多,直到组件达到回流温度曲线的液化区域。快速干燥的醇基助焊剂可能要求芯片贴装之前分阶段处理。

为了充分利用贴装单元,上助焊剂是使用一台专用的滴胶机在芯片贴装之前完成的。没有采用诸如压印 (stamping) 、浸 (dipping) 或刷 (brushing) 等接触式方法,由于产品专门的定位装置和对污染的关注。

量的控制是助焊剂滴涂的最重要方面。要求最少的量是百分之百的覆盖锡球座 / 滑道 (site/runner) 。不完全覆盖将造成电气开路和装配的报废。增加的量超过了百分之百的要求将改善粘着性能,但可能反过来影响产品的可靠性。过多的助焊剂可能造成回流焊后的残留物和不希望的区域侵蚀。有机残留物对底部充胶是有害的,降低系统的现场可靠性。助焊剂迁移或流动超出芯片座可能引起焊锡球 (solder ball) 、组件竖立 (tombstoning) 和 PCB 的离子污染 (ionic contamination) 。对每个产品的最后量的规定必须平衡百分之百覆盖要求、最大粘着性能、最少助焊剂残留物和组件偏移控制。

上助焊剂不要求很高的放置精度。使用两个全局基准点作板的定位,可得到很高的可信水平。对每个贴片座的局部基准点是没有必要的,它会降低设备周期。设备购买时不能没有视觉系统,但多数便利设施可以省去 - 快速简便的产品编程和设定确认等。

芯片贴装 (die placement)

芯片贴装容易实施,因为设备对工厂人员都很熟悉。设备具有 C4 倒装芯片贴装头,只用于 IC 的贴装。贴装头有四个贴装转轴 (spindle) ,维持 X-Y 贴装精度为± 200 µ m 和最大贴装力为 2500g 。芯片以盘带包装,用黑色叠尔林 (Delrin) 吸嘴来吸取组件。

通常,贴装压力应该为每个 I/O 6~ 12g 。在这种情况下, 100 I/O 要求 600~ 1200g 之间的压力。过大贴装压力有一个缺点,尽管贴装头 / 视觉系统扫描后已经作了纠正,贴装压力可能产生组件偏移。还有,如果托盘的刚性不够,或者板的支撑不正确,贴装时板可能会向下弯曲。

组件的视觉识别路线设定是,沿芯片周围识别 48 个锡球 (bump) ,和中间附近一个定向锡球。锡球的数量经过优化达到最高的贴装精度和最大的机器产量。增加锡球数量大大地延长处理时间,而贴装精度保持不变。

一个分辨率为每个象素 1.3mil 的相机用来抓拍芯片的图像。通过二级光强度的侧光,得到足够的对比度。贴装单元也配备一个每个象素 0.5mil 的可选相机,但要求抓拍两个芯片图像。

用三个全局基准点来决定 PCB 和贴装座的位置。基准点应该是金属作的,以保证锡球的贴放是相对于倒装芯片的焊盘,而不是阻焊层。

贴装之后、回流之前板的所有运动和传送必须平滑,不能影响组件的定位。如果组件的移位元是来自贴装单元,那么机器传送带、升起定位和 Z- 轴的加速度和速度的设定可能需要降低。在高速运作期间,也必须使用适当的板支撑,以减少 PCB 挠曲。挠曲或反回可能引起前面贴装的芯片移出焊盘,特别是如果在表面贴装之前数组 (array) 翘曲。

回流 (Reflow)

在贴装工艺之后,装配通过一个空气对流炉,来回流共晶焊锡球,形成电气连接。炉设定按标准的表面贴装温度曲线。氮气流速提供良好的热传导,限制氧气污染。炉的进口处过大的氮气流速可能引起芯片偏移出焊盘,因此引发缺陷。如果这个偏移变成一个长期的问题,可增加分流板来防止气流直接冲击芯片。开始的温度斜率不应该超过每秒 1.5~ 2.0 ° C 。高的预热速率迅速蒸发助焊剂,引起回流焊接之前芯片偏移,甚至翻转。

每个产品都必须作温度曲线,以保证满足适当的回流条件。在生产线预防性维护或板有任何改动之后,应该再作温度曲线。表面上不重要的修改,如改变地线层的尺寸或位置,可影响热传递速率和倒装芯片的回流。氮气流速使用安装在炉前的流量计来监测。氧气水平可用也是安装在炉前的探测器来检查。

先进先出 (FIFO, first-in, first-out) 的缓冲器应该安装在回流炉的立即出口,在底部充胶单元之前。这个预防措施将收在集流水线关闭期间正在回流炉内的任何电路板。

底部充胶 (Underfill)

底部充胶对倒装芯片装配的长期可靠性是必须的。胶减少焊接点的应力,将应力均匀地分散在倒装芯片的接口上。每个充胶系统的可靠性可能差别很大,决定于倒装芯片装配的结构;因素包括离板间隙 (standoff) 高度、芯片钝化、阻焊剂供货商和 PCB 材料。所希望的制造特性包括快速的流动速率、快速固化、长的储存稳定性和容易使用到倒装芯片座。为了达到成功,充胶的附着、颗粒尺寸分布和填充量必须修整,以满足制造和可靠性要求。

多数充胶材料是基于环氧树脂的系统,充入 50~70% 重量的硅来协调稳定膨胀系数 (CTE, coefficient of thermal expansion) 。所有元素预先混合包装在注射器内,适于所希望的速率和材料储存寿命。注射器大小应该限制操作员的干涉时间为每四到八个小时,因此减少停线期间的材料浪费,但又不太影响产量。

充胶材料储存在 -40 ° C 的冷冻机内,在装上滴胶机之前,解冻至少 30 分钟。解冻到一个稳定的稳定状态,防止不利的粘度变化,它会引起充胶量的变化。充胶的制造储存寿命应该至少四小时。在这个时间内,滴胶机应该展示连续的胶流、无针嘴滴漏 (dripping/drool) 和良好的滴胶点尾的断开。超过材料储存寿命可能造成充胶不完整和低劣的附着。

用旋转式胶泵将胶填充到基板。这个阀是坚固的,易于清洁,并可在胶剂寿命内滴出连续一致的胶量。基板温度是不受控制的,其变化决定于经过回流炉之后所持续的时间。胶剂是以充胶到芯片所有四条边的形式滴注的。这种形式提供良好的圆角成型,并且比曾经评估过的单线或 L 形滴胶更快速。

在滴胶之前,用设备的视觉程序来定位 IC 的每条边,减少滴胶嘴由于移位元的芯片而被弯曲的机会。损坏的滴胶嘴将不会正确地滴胶,在发觉之前可能引起无数的缺陷。柔性的滴胶嘴是个可接受的替代者,如果视觉要求反过来影响设备的产量。柔性的滴胶嘴在受冲击时会弯曲,但是如果滴胶嘴变形,滴胶精度可能受影响。

芯片周围 1~ 2mm 的组件非入区是所希望的,但并不一定总是可行的,因为设计的局限。在本文所述的情况中,有热封装配、一个开关和几个离散组件处在非入区的里面或附近。滴在或流入热封组件和开关区域的胶可能毁坏整个 PCB 。密封的离散组件不会负面影响射频性能,但将抑制芯片下的胶流。这些组件也将在固化后永久地绑接在位置上,可能使得竖立的电容无法修理。 12~16mg 的底部充胶提供必要的覆盖并限制污染。

固化 (cure)

底部充胶的装配通过一个固化炉,使胶剂聚合。卧式、立式和微波炉都可使用,决定于应用和固化时间的要求:

- 卧式固化炉,成本低、到处都可找到、可靠、也提供作为回流焊炉的双重功能。立式与微波炉通常是专门的固化炉,不能用于回流。

- 立式炉具有高容量,占地面积小,但复杂性增加可能导致可靠性和维护等问题。

- 微波炉提供快速的批量处理,但大大增加固定资产成本。从产品到产品来作炉的温度曲线也变得更困难。

5~15 分钟的充胶固化时间允许标准的卧式回流焊炉当作固化炉用。为了增加能力,将炉由单轨信道改为双轨信道。这个修改改进了利用率,消除了每条线多个固化炉的需要。

固化缺陷是一个关注,因为它们可能不被发觉,直到寻呼机到了顾客手中。开始的升温速率和温度上的时间 (time-at-temperature) 是重要的温度曲线参数,必须得到控制。过快的升温速度可能引起充胶的过早凝固,或者在系统中挥发低分子重量的单分子物体。过早的凝固在它适当地密封芯片之前就停止了材料流动,挥发的单分子物体将造成空洞。这两种情况都是不可接受的,并诱发可靠性问题。维持特定的固化时间和温度对充胶达到其完全功能是必须的。充胶的温度记录决定其物理特性,如玻璃态转化温度、 CTE 、粘着力和吸潮特性。加热时间不充分将造成不适当聚合的胶体,可能不能提供足够的完整的机械特性。

结论

工程师在实施一项倒装芯片应用时,应该应用两条设计规则:

- 限制倒装芯片将要经受的静态和动态的电路板弯曲。将芯片贴放在诸如螺钉头或键盘区域背面等高应力点,可能导致底部充胶的脱层和潜在的现场失效。

- 避免芯片背面可能受到冲击的区域。如有必要,增加一个冲击垫或盖来限制 IC 断裂或碎裂。

遵守这些规则将改善最后装配的可靠性,和避免潜在的现场失效。技术进步继续推动倒装芯片装配迈向表面贴装制造的主流。在许多领域的发展,如无流动 (no-flow) 低部充胶 (underfill) 、低成本 HDI 基板和高精度贴片设备,将继续降低成本和消除实施倒装芯片技术的障碍。