新型的倒装芯片 ACF 贴装技术

By 张兴隆

本文着重讨论了在倒装芯片组装中采用新型“有序” ACF 的优点。特别地,导电粒子的分布取决于倒装芯片凸点,并且与理论推论相吻合。

用各向异性导电胶 (ACF) 作为互连材料贴装硅芯片并不是一种新方法,早已被普遍用于倒装芯片与玻璃的连接上。但是,传统的 ACF 有一个重要的缺点,即内部导电粒子的分布是无序的。那就意味着大量的导电粒子存在于两个连接面间,且呈不均匀状态分布,而这一不均匀性最坏情况下会导致开路或短路。而最大的可能是导致接触电阻的不同。接触电阻的不同在 FCOG 场合下是允许的,因为整个电路的电阻很大。但是在其它情况下 ( 如刚性或柔性有机基板 ) 接触电阻差别过大是不可接受的。因此,理想的倒装芯片互联材料其导电粒子的分布应是均匀的,以保证在每个焊盘上的数量相同。随着面阵凸点芯片的日益普及,对于导电粒子均匀程度的要求也将更为严格。目前新材料正在实际生产中试用,以确认其优越性。

ACF 的特性

ACF 材料是采用特殊技术制成,以使任一单分散性导电粒子均匀分布。在研究的初期采用的是单分散性的镀金的聚合物球(直径 7 μ m )。黏着剂采用环氧树脂及微量的电子级质量化学药品。 ACF 材料的典型性能见表 1 。

表 1 : ACF 材料的特性。

本文主要就一种载体含量为 1800 粒 /mm2 的 ACF 材料进行讨论。该载体适用于本次研究的凸点间距。同样也能生产出更高颗粒密度的材料,导电粒子独立分布,但此时的平均间距缩小了。高密度材料适用于细间距电路。

评估技术

图像分析可用来分析实际倒装芯片组件上每一凸点处颗粒的平均数量。例如,组件有 98 个球形凸点 (100 μ m×100 μ m , 20 μ m 高 ) ,间距 200 μ m 。组件置于 ITO 玻璃基板上,以使凸点区域显露出来,从而能够进行图像分析。

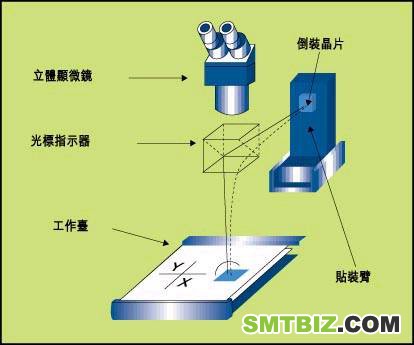

图像分析系统包括一个高质量的反射显微镜,显微镜与一个高分辨率的 CCD 摄像机及一台装有图像分析软件的计算机相连。倒装芯片的连接用一台 Finetech Fineplacer 183 倒装芯片邦定机 ( 如图 1) 黏着。

图 1 :具有 5 μ m 以上贴装精度的 Finetech Fineplacer 183 邦定机。

这是一台手动系统,贴装精度可达 5 μ m 以上,包括一黏着于支点上的贴装臂和装于气垫上的工作台,贴装臂上装有带加热与真空装置的定心爪。用真空吸取倒装芯片,经定心爪定心后,藉由立体显微镜和一个固定光标指示器,与台上的基板对准。基板能够作 X 、 Y 与θ方向的移动以准确定位。随后贴装臂转动 90° 使芯片装贴于基板上。然后再在其上施加不同的温度和压力以形成可靠的连接。通常以 180 ℃ 的温度加热至少 20 秒的时间,压力应根据凸点面积的不同可在 1 至 50MPa 间改变。

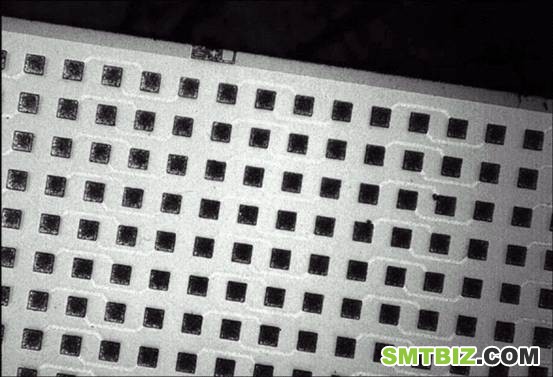

在本试验方案中,第二种倒装芯片用于对有序 ACF 的电气性能进行评估。该芯片有 576 个凸点以面阵式排列 ( 见图 2) 。凸点尺寸依然是 100 μ m ,间距 200 μ m 。

图 2 :用于对“有序” ACF 进行评估的面阵式倒装芯片。

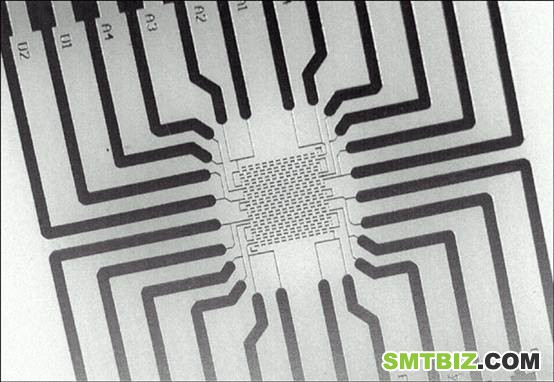

相应的 FR4 基板如图 3 。

图 3 :面阵式 FR4 基板上各种纽链式结构。

当凸点被压入膜中至相应值时,少量的胶便会被置换出来。凸点所占总面积为 0.0196mm 2 ,仅为芯片下胶面积的 3%( 芯片尺寸为 5mm × 5mm , ACF 厚度为 25 μ m) 。由于被置换出的量极少,因此装配时不会对相邻凸点造成破坏。

如果采用较厚的膜,便会出现更多的损坏,原因是在凸点尚未与导电粒子相接触时,大量的胶便已被置换出来,芯片下胶的“流动”会导致粒子顺序的破坏。可以预见对于面阵芯片结构,在 ACF 厚度与胶体的流动 / 导电粒子运动间有一些关系,一旦在玻璃基板上的试验结束,这些关系便会被揭示出来。

基板的共面性同样对装贴后导电粒子的分布有影响。 ITO 玻璃基板是非常理想的选择因为其表面非常平整。在周边凸点芯片和面阵凸点芯片上的电性能试验已完成,组件在各种老化条件下长期可靠性试验后的接触电阻值与芯片的初始接触电阻值基本相同。

一种新颖的 ACF 能使所有导电粒子均匀分布。在倒装芯片装联时采用这种材料,可将凸点下导电粒子数量的实际值达到理论值的水平。但是, ACF 的厚度必须优化为凸点高度,以保证导电粒子的顺序不会被破坏。

倒装芯片下填充的选择

在不考虑其它因素时,影响倒装芯片封装可靠性的关键是所使用的下填充材料。正确选择下填充材料时应考虑以下因素:如热胀系统、黏度、流动性、模量与黏性。

用导电聚合体进行倒装芯片的连接

在倒装芯片上采用导电聚合凸点对减少组装体积、提高组装密度、电气速度与生产效率非常有利。

倒装芯片下填充增强其热可靠性

采用面阵式封装可以满足器件对于多引脚、高密度与高性能的要求。了解下填充制程和相关参数有助于获得足够的组装可靠性。

先进的 IC 驱动着 Post-fab 的变化 对于新型生产技术影响的讨论大多关注于印刷和互联技术。事实上,新技术在半导体生产制程方面对 post-fab 的影响已经产生,只是在生产作业方面没有明显变化而已。